- 基于Step-Mxo2-LCP的3-8译码器

城里有一颗星星

FPGA基础模块fpga开发fpga笔记

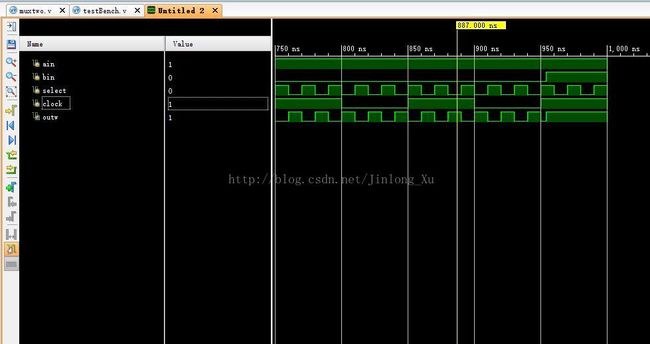

译码器的基本概念:译码器的逻辑功能是将每个输入的二进制代码译成对应的输出高、低电平信号或另外一个代码。一般有二进制译码器、二-十进制译码器和显示译码器。二进制译码器:二进制译码器的输入是一组二进制代码,输出是一组与输入代码一一对应的高、低电平信号。Verilog代码1:每一个输入代码译成对应输出端的低电平信号,LED1~LED8,输出对应的LED灯为亮/*3-8译码器*/moduledecode3

- verilog中何时使用begin—end

0基础学习者

verilog学习数字icverilogfpga

当条件语句(如if,elseif,或者case)后面只有一条语句时,可以直接书写该语句而无需使用begin和end。然而,如果需要执行多条语句,则必须通过begin和end将这些语句组合成一个块状结构。使用begin和end的情况:always@(posedgeclkornegedgereset_n)beginif(!reset_n)begin//这里if下面执行了两句话所以需要再if语句里面再嵌

- [AI速读]CHISEL vs. SystemVerilog:用RISC-V核心对比两种硬件设计语言

iccnewer

risc-v设计语言

在硬件设计领域,选择合适的语言对开发效率、维护成本和最终性能都至关重要。最近,一项研究对比了两种硬件描述语言——CHISEL(基于Scala的嵌入式语言)和传统的SystemVerilog,它们分别实现了同一款RISC-V核心(SweRV-EL2)。以下是关键发现和结论。为什么选择CHISEL?CHISEL是一种基于Scala的高级硬件构造语言,它结合了面向对象和函数式编程的特性。与传统的Syst

- FPGA实战1-流水灯实验verilog

马志高

FPGAfpga开发

1.实验要求(1)设计一个流水灯的实验,实现12位流水灯的依次点亮,(2)流水灯的流转时间是(500ms/2Hz),(3)系统时钟位50MHz,(4)定义12个寄存器ledtemp保存12个状态,(5)寄存器的初始值位12'b0000_0000_0001,(6)当移位到12‘b1000_0000_0000时,ledtemp的值回到12'b0000_0000_0001,2.设计代码//coding/

- 【从零开始学习计算机科学】计算机体系结构(一)计算机体系结构、指令、指令集(ISA)与量化评估

贫苦游商

学习服务器网络计算机体系结构ISA指令集量化评估

【从零开始学习计算机科学】计算机体系结构(一)计算机体系结构、指令、指令集(ISA)与量化评估概论计算机体系结构简介计算机的分类并行体系结构指令集体系结构(ISA)分类存储器寻址寻址模式操作数大小指令ISA的编码程序的优化计算机体系结构量化评估存储器体系结构概论计算机体系结构与计算机组成原理之间的联系非常紧密,其研究范畴基本一致,计算机体系结构与计算机组成原理两者是相辅相成的。但是,计算机体系结构

- 指令系统和计算机体系结构——一文解析冯·诺依曼架构

点滴汇聚江河

软考-软件设计师架构

文章目录一、核心思想二、核心组成部分1.中央处理器(CPU)2.内存(Memory)3.输入/输出(I/O)设备4.总线(Bus)三、工作流程四、冯·诺依曼架构的局限性五、现代计算机的改进1.流水线技术(Pipeline)关键机制2.高速缓存(Cache)关键机制3.多核CPU(Multi-Core)关键挑战与解决方案4.乱序执行(Out-of-OrderExecution)关键技术5.其他关键改

- 单端口和双单口RAM的实现

wangn1633

Verilogverilog

单端口和双单口RAM的verilog实现概念:1单端口:读写数据共用一个地址线,一个时钟沿只能进行读或者写;2伪双端口:写数据和读数据有自己的地址、时钟、读写使能信号;也就是一组端口只能写,一组端口只能读。(读写数据也可共用一个clk,为同步伪双端口ram)3真双端口:一组端口可读可写,另一组端口也可读可写。(若这两组端口共用一个clk,为同步真双端口ram。若每组有每组的clk,为异步真双端口r

- FPGA中级项目3——IP核之时钟管理单元

霖00

fpga开发经验分享嵌入式硬件fpga网络时序数据库

FPGA中级项目3——IP核之时钟管理单元时钟还需要管理?什么是时钟管理单元?我们常熟知FPGA本身有晶振单元,源源不断的提供的50Mhz的频率波。但是这样往往无法满足一些设计需求。使用Verilog代码设计倍频分频等又不可避免的出现毛刺等其他状况,且提升了代码复杂度。因此在FPGA设计中,时钟管理单元(ClockManagementUnit,CMU)IP核是关键组件,用于生成、调整和分配系统时钟

- Lua语言的计算机体系结构

凌嘉遥

包罗万象golang开发语言后端

Lua语言的计算机体系结构引言Lua是一种轻量级、高效且可扩展的脚本语言,最早由巴西的一个小组开发。它的设计目标是为嵌入式系统提供一个简洁的语言,从而使开发者能够在不同的应用程序中方便地进行扩展和集成。尽管Lua本身是一种面向过程的语言,但它也支持面向对象编程、函数式编程等多种编程范式。因此,研究Lua的计算机体系结构,不仅能帮助我们理解Lua如何实现其功能,还能为其他编程语言的设计与实现提供参考

- 【从零开始学习计算机科学】数字逻辑(四)数字系统设计

贫苦游商

学习数字逻辑verilog数字系统HDL数字电路FPGA

【从零开始学习计算机科学】数字逻辑(四)数字系统设计数字系统设计硬件描述语言HDL(HardwareDescriptionLanguage)VerilogHDL的起源与发展HDL软核、固核和硬核的重用HDL的应用数字系统设计实现数字系统设计一个数字集成电路的可以从不同的层次(系统级、算法级、寄存器传输级、门级、开关级)以及不同的领域(行为领域、结构领域、物理领域)进行描述。三个领域主要含义如下:行

- 用 Verilog 实现 0 到 18 计数器:从原理到实践的全解析

君临天下.鑫

modelsim波形仿真verilogfpga开发课程设计经验分享笔记编辑器

在数字电路设计中,计数器是极为重要的基础部件,广泛应用于各类数字系统。本次实验聚焦于设计一个从0到18计数的计数器,通过深入探索计数器的工作原理、利用组合逻辑控制计数范围,进一步加深对数字电路和Verilog语言的理解与应用。一、实验目的理解计数器通用原理:全面掌握计数器的基本工作原理,包括计数的方式、状态的转换以及与外部信号的交互等,为设计特定功能的计数器奠定理论基础。运用组合逻辑控制计数范围:

- 计算机体系结构的五大流派,你知道几个?

绿算技术

计算机五大流派https信息与通信硬件工程缓存

在计算机的世界里,架构设计是决定性能和应用场景的关键。从经典的冯·诺依曼结构到现代的并行处理结构,每一种体系结构都有其独特的优势和适用场景。今天,我们绿算与大家一起聊聊计算机体系结构的五大流派,以及它们背后的厂商和应用领域。1.冯·诺依曼结构:现代计算机的基石冯·诺依曼结构是现代计算机的基础,几乎所有通用计算机系统都基于这一结构或其变体。它的核心特点是程序和数据共享同一存储空间,通过一条总线进行传

- FPGA 学习笔记:Vivado 2020.2 MicroBlaze MIG 测试 DDR3 篇二

zhangsz_sh

FPGA开发技术fpga开发学习

前言因为FPGADDR3测试的工程搭建步骤比较的多,所以分成几篇来写,这样利于把复杂的事情拆分,利于理解与实际的操作上一篇搭建了初步的HelloWorld工程,还没写什么代码或者改什么配置,所以FPGA开发,并不是上来就写VerilogHDL,而是要把更多的时间用在:目标是什么?DDR3测试,正常DDR3能否当RAM一样使用清楚要做什么,这里通过搭建嵌入式软核处理器的方式,快速验证实现与验证:搭建

- 基于 Verilog 的经典数字电路设计(1)加法器

新芯设计

1专栏革新中禁止订阅!!!FPGAVerilog加法器数字IC设计IC

基于Verilog的经典数字电路设计(1)加法器版权所有,新芯设计,转载文章,请注来源引言一、半加器的Verilog代码实现和RTL电路实现一、全加器的Verilog代码实现和RTL电路实现引言 加法器是非常重要的,它不仅是其它复杂算术运算的基础,也是CPU中ALU的核心部件(全加器)。两个二进制数之间的算术逻辑运算例如加减乘除,在数字计算机中都是化为若干步加法操作进行的,因此,学好数字电路,从

- FPGA学习——verilog捕捉信号上升沿下降沿

or_to

FPGAfpga开发学习

在FPGA使用中,常常需要进行信号的边沿检测,如在串口通信中,需要检测接收信号的下降沿来判断串口的的起始位。常用的方法就是:设计两个一位的寄存器,用来接收被检测的信号,系统时钟来一次记一次输入信号,如果用了两个寄存器直接异或就可以了;使用高频的时钟对信号进行采样,因此要实现上升沿检测,时钟频率至少要在信号最高频率的2倍以上,否则就可能出现漏检测。代码如下:moduleedge_detect(sys

- FPGA学习篇——Verilog学习4(常见语句)

ooo-p

Verilog学习fpga开发学习

1.1结构语句结构语句主要是initial语句和always语句,initial语句它在模块中只执行一次,而always语句则不断重复执行,以下是一个比较好解释的图:(图片来源于知乎博主罗成,画的很好很直观!)1.1.1initial语句initial语句它在模块中只执行一次。它常用于测试文件的编写,用来产生仿真测试信号(激励信号),或者用于对存储器变量赋初值。语法格式:initialbegin.

- FPGA学习笔记(二)Verilog语法初步学习(语法篇1)

贾saisai

FPGA学习fpga开发学习1024程序员节

FPGA系列文章目录一、FPGA学习笔记(一)入门背景、软件及时钟约束二、FPGA学习笔记(二)Verilog语法初步学习(语法篇1)三、FPGA学习笔记(三)流水灯入门FPGA设计流程四、FPGA学习笔记(四)通过数码管学习顶层模块和例化的编写五、FPGA学习笔记(五)Testbench(测试平台)文件编写进行Modelsim仿真六、FPGA学习笔记(六)Modelsim单独仿真和Quartus

- Verilog学习方法—基础入门篇(一)

博览鸿蒙

FPGAfpga开发

前言:在FPGA开发中,VerilogHDL(硬件描述语言)是工程师必须掌握的一项基础技能。它不仅用于描述数字电路,还广泛应用于FPGA的逻辑设计与验证。对于初学者来说,掌握Verilog的核心概念和基本语法,是深入FPGA开发的第一步。本篇文章将从Verilog基础入门的角度,帮助你快速建立学习框架,逐步掌握Verilog的使用方法。1.了解Verilog的基本概念1.1什么是Verilog?V

- 【从零开始学习计算机科学】数字逻辑(五) Verilog HDL语言

贫苦游商

学习fpga开发数字逻辑verilogHDL硬件开发逻辑电路

【从零开始学习计算机科学】数字逻辑(五)VerilogHDL语言VerilogHDL语言8位全加器8位计数器2位比较器三态驱动器VerilogHDL模块的结构模块声明。端口定义。信号类型。功能描述verilog描述级别verilog关键字verilog标识符编写VerilogHDL源代码的标准数据类型常量变量nets型变量register型变量reg型变量运算符及表达式算术运算符逻辑运算符位运算符

- 基于FPGA的图像中值滤波Verilog实现及MATLAB辅助验证

CodeWG

fpga开发matlab开发语言

基于FPGA的图像中值滤波Verilog实现及MATLAB辅助验证图像处理是计算机视觉和图像识别领域的重要组成部分。其中,中值滤波是一种常用的图像去噪方法,广泛应用于图像增强、边缘检测和特征提取等任务中。本文将介绍基于FPGA的图像中值滤波Verilog实现,并通过MATLAB进行辅助验证。首先,我们需要了解什么是中值滤波。中值滤波是一种非线性滤波器,它的原理是将图像中每个像素的灰度值替换为该像素

- verilog练习:HRPWM 模块设计

啄缘之间

Verilog项目练习学习资料总结fpga开发学习svuvmverilog测试用例

文章目录前言1.HRPWM代码示例:1.1关键设计说明:2.HRPWM温度补偿和动态校准2.1关键增强功能说明:2.2校准流程验证方法:2.3性能优化建议:前言需要考虑如何用SystemVerilog实现这些功能。首先,模块的输入输出端口应包括时钟、复位、占空比设置、使能信号,以及PWM输出。内部可能需要计数器、比较寄存器、MEP控制逻辑。MEP的实现可能需要一个微边沿计数器,在每个主时钟周期内生

- 用verilog实现3-8译码器和全加器

珠泪美人鱼

fpga开发

提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档文章目录前言一、pandas是什么?二、使用步骤1.引入库2.读入数据总结提示:以下是本篇文章正文内容,下面案例可供参考一、用verilog实现3-8译码器首先在一个磁盘上创建一个文档。如下图:在文档中在创建两个文档来储存项目和代码。如图:之后在quartus上建好项目后,填写代码。代码如图:

- 【HDLbits--FSM状态机】

中古传奇

HDLHDL

HDLbits--FSM状态机1.6FSM介绍1.6FSM示例1单输入单输出FSM2双输入单输出FSM3真指标状态4MooreFSMdemo5时序图和状态图写状态机【博客首发于微信公众号《漫谈芯片与编程》,欢迎大家关注,多谢大家】1.6FSM介绍在Verilog中,有限状态机(FiniteStateMachine,FSM)是一种用于描述系统行为的模型,通常用于控制逻辑的设计。FSM由一组状态、状态

- 验证环境中为什么要用virtual interface

m0_71354184

systemverilog

在UVM(UniversalVerificationMethodology)中使用virtualinterface的主要目的是解决SystemVerilog接口(interface)的静态特性与UVM验证环境的动态特性之间的不匹配问题。1.解决静态与动态的绑定问题SystemVerilog接口(interface)是静态的:在编译时确定,无法直接用于动态创建的UVM对象(如driver、monit

- 6. 示例:用mailbox实现生产者-消费者模型

啄缘之间

UVM学习计划表学习verilog测试用例svuvm

文章目录前言示例一:生产者-消费者模型1示例二:生产者-消费者模型2示例三:生产者-消费者模型3示例四:生产者-消费者模型41.完整代码示例2.仿真步骤3.关键代码解析4.波形与日志分析5.常见问题与解决6.扩展练习前言以下是一个完整的SystemVerilog示例,使用mailbox实现生产者-消费者模型,包含详细注释、仿真步骤及预期结果。代码兼容主流仿真工具(如CadenceXcelium的x

- 【Verilog--Procedures】

中古传奇

HDLHDL

Verilog--Procedures1.4Procedures1.4.0CombVSClocked1.4.1always-if1.4.1.1Avoidlatches1.4.2case【博客首发于微信公众号《漫谈芯片与编程》,欢迎大家关注,多谢大家】电路模块是由通过导线连接的逻辑门组成,任何电路都可以表示为模块和赋值语句的某种组合。但有时候这不是描述电路的方便方法。过程(其中always是一个例子

- Linux下VCS与Verdi联合仿真(Verilog与VHDL混仿)

超能力MAX

fpga开发

1.介绍本篇简单介绍一下如何通过VCS与Verdi实现混合仿真,在学习过程中也遇到了很多头疼的问题,因此通过一些例子简要总结一下,当然,也希望对各位小伙伴有所帮助。很多公司ASIC设计所使用的还是更加专业的EDA软件,即Synopsys下的VCS、Verdi这种(Vivado大多针对于自家FPGA),VCS编译速度极快,仿真效率高,Verdi支持信号追溯、无缝增加信号波形等功能。2.使用环境:Li

- FPGA基础知识----第三章 第2节 综合和仿真

原来如此呀

FPGA学习之旅fpgaverilog

第2节综合和仿真2.1综合Verilog是硬件描述语言,顾名思义,就是用代码的形式描述硬件的功能,最终在硬件电路上实现该功能。在Verilog描述出硬件功能后需要使用综合器对Verilog代码进行解释并将代码转化成实际的电路来表示,最终产生实际的电路,也被称为网表。这种**将Verilog代码转成网表的工具就是综合器**。上图左上角是一段Verilog代码,该代码实现了一个加法器的功能。在经过综合

- (14)FPGA与GPU区别

宁静致远dream

FPGA入门与提升(培训课程)fpga开发

(14)FPGA与GPU区别1文章目录1)文章目录2)FPGA入门与提升课程介绍3)FPGA简介4)FPGA与GPU区别5)技术交流6)参考资料2FPGA入门与提升课程介绍1)FPGA入门与提升文章目的是为了让想学FPGA的小伙伴快速入门以及能力提升;2)FPGA基础知识;3)VerilogHDL基本语法;4)FPGA入门实例;5)FPGA设计输入,包括代码输入、原语输入;6)FPGA设计技巧;7

- lattice hdl实现spi接口

寒听雪落

FPGA专栏_verilogfpga开发

在lattice工具链中实现SPI接口通常涉及以下步骤:定义硬件SPI接口的管脚。配置SPI时钟和模式。编写SPI主机或从机的控制逻辑。展示了如何在Lattice工具链中使用HDL语言(例如Verilog)来配置SPI接口:lattice工程顶层:spi_slave_top.v`timescale1ns/1psmodulespi_slave_top(inputwireCLK,//Systemclo

- Enum 枚举

120153216

enum枚举

原文地址:http://www.cnblogs.com/Kavlez/p/4268601.html Enumeration

于Java 1.5增加的enum type...enum type是由一组固定的常量组成的类型,比如四个季节、扑克花色。在出现enum type之前,通常用一组int常量表示枚举类型。比如这样:

public static final int APPLE_FUJI = 0

- Java8简明教程

bijian1013

javajdk1.8

Java 8已于2014年3月18日正式发布了,新版本带来了诸多改进,包括Lambda表达式、Streams、日期时间API等等。本文就带你领略Java 8的全新特性。

一.允许在接口中有默认方法实现

Java 8 允许我们使用default关键字,为接口声明添

- Oracle表维护 快速备份删除数据

cuisuqiang

oracle索引快速备份删除

我知道oracle表分区,不过那是数据库设计阶段的事情,目前是远水解不了近渴。

当前的数据库表,要求保留一个月数据,且表存在大量录入更新,不存在程序删除。

为了解决频繁查询和更新的瓶颈,我在oracle内根据需要创建了索引。但是随着数据量的增加,一个半月数据就要超千万,此时就算有索引,对高并发的查询和更新来说,让然有所拖累。

为了解决这个问题,我一般一个月会进行一次数据库维护,主要工作就是备

- java多态内存分析

麦田的设计者

java内存分析多态原理接口和抽象类

“ 时针如果可以回头,熟悉那张脸,重温嬉戏这乐园,墙壁的松脱涂鸦已经褪色才明白存在的价值归于记忆。街角小店尚存在吗?这大时代会不会牵挂,过去现在花开怎么会等待。

但有种意外不管痛不痛都有伤害,光阴远远离开,那笑声徘徊与脑海。但这一秒可笑不再可爱,当天心

- Xshell实现Windows上传文件到Linux主机

被触发

windows

经常有这样的需求,我们在Windows下载的软件包,如何上传到远程Linux主机上?还有如何从Linux主机下载软件包到Windows下;之前我的做法现在看来好笨好繁琐,不过也达到了目的,笨人有本方法嘛;

我是怎么操作的:

1、打开一台本地Linux虚拟机,使用mount 挂载Windows的共享文件夹到Linux上,然后拷贝数据到Linux虚拟机里面;(经常第一步都不顺利,无法挂载Windo

- 类的加载ClassLoader

肆无忌惮_

ClassLoader

类加载器ClassLoader是用来将java的类加载到虚拟机中,类加载器负责读取class字节文件到内存中,并将它转为Class的对象(类对象),通过此实例的 newInstance()方法就可以创建出该类的一个对象。

其中重要的方法为findClass(String name)。

如何写一个自己的类加载器呢?

首先写一个便于测试的类Student

- html5写的玫瑰花

知了ing

html5

<html>

<head>

<title>I Love You!</title>

<meta charset="utf-8" />

</head>

<body>

<canvas id="c"></canvas>

- google的ConcurrentLinkedHashmap源代码解析

矮蛋蛋

LRU

原文地址:

http://janeky.iteye.com/blog/1534352

简述

ConcurrentLinkedHashMap 是google团队提供的一个容器。它有什么用呢?其实它本身是对

ConcurrentHashMap的封装,可以用来实现一个基于LRU策略的缓存。详细介绍可以参见

http://code.google.com/p/concurrentlinke

- webservice获取访问服务的ip地址

alleni123

webservice

1. 首先注入javax.xml.ws.WebServiceContext,

@Resource

private WebServiceContext context;

2. 在方法中获取交换请求的对象。

javax.xml.ws.handler.MessageContext mc=context.getMessageContext();

com.sun.net.http

- 菜鸟的java基础提升之道——————>是否值得拥有

百合不是茶

1,c++,java是面向对象编程的语言,将万事万物都看成是对象;java做一件事情关注的是人物,java是c++继承过来的,java没有直接更改地址的权限但是可以通过引用来传值操作地址,java也没有c++中繁琐的操作,java以其优越的可移植型,平台的安全型,高效性赢得了广泛的认同,全世界越来越多的人去学习java,我也是其中的一员

java组成:

- 通过修改Linux服务自动启动指定应用程序

bijian1013

linux

Linux中修改系统服务的命令是chkconfig (check config),命令的详细解释如下: chkconfig

功能说明:检查,设置系统的各种服务。

语 法:chkconfig [ -- add][ -- del][ -- list][系统服务] 或 chkconfig [ -- level <</SPAN>

- spring拦截器的一个简单实例

bijian1013

javaspring拦截器Interceptor

Purview接口

package aop;

public interface Purview {

void checkLogin();

}

Purview接口的实现类PurviesImpl.java

package aop;

public class PurviewImpl implements Purview {

public void check

- [Velocity二]自定义Velocity指令

bit1129

velocity

什么是Velocity指令

在Velocity中,#set,#if, #foreach, #elseif, #parse等,以#开头的称之为指令,Velocity内置的这些指令可以用来做赋值,条件判断,循环控制等脚本语言必备的逻辑控制等语句,Velocity的指令是可扩展的,即用户可以根据实际的需要自定义Velocity指令

自定义指令(Directive)的一般步骤

&nbs

- 【Hive十】Programming Hive学习笔记

bit1129

programming

第二章 Getting Started

1.Hive最大的局限性是什么?一是不支持行级别的增删改(insert, delete, update)二是查询性能非常差(基于Hadoop MapReduce),不适合延迟小的交互式任务三是不支持事务2. Hive MetaStore是干什么的?Hive persists table schemas and other system metadata.

- nginx有选择性进行限制

ronin47

nginx 动静 限制

http {

limit_conn_zone $binary_remote_addr zone=addr:10m;

limit_req_zone $binary_remote_addr zone=one:10m rate=5r/s;...

server {...

location ~.*\.(gif|png|css|js|icon)$ {

- java-4.-在二元树中找出和为某一值的所有路径 .

bylijinnan

java

/*

* 0.use a TwoWayLinkedList to store the path.when the node can't be path,you should/can delete it.

* 1.curSum==exceptedSum:if the lastNode is TreeNode,printPath();delete the node otherwise

- Netty学习笔记

bylijinnan

javanetty

本文是阅读以下两篇文章时:

http://seeallhearall.blogspot.com/2012/05/netty-tutorial-part-1-introduction-to.html

http://seeallhearall.blogspot.com/2012/06/netty-tutorial-part-15-on-channel.html

我的一些笔记

===

- js获取项目路径

cngolon

js

//js获取项目根路径,如: http://localhost:8083/uimcardprj

function getRootPath(){

//获取当前网址,如: http://localhost:8083/uimcardprj/share/meun.jsp

var curWwwPath=window.document.locati

- oracle 的性能优化

cuishikuan

oracleSQL Server

在网上搜索了一些Oracle性能优化的文章,为了更加深层次的巩固[边写边记],也为了可以随时查看,所以发表这篇文章。

1.ORACLE采用自下而上的顺序解析WHERE子句,根据这个原理,表之间的连接必须写在其他WHERE条件之前,那些可以过滤掉最大数量记录的条件必须写在WHERE子句的末尾。(这点本人曾经做过实例验证过,的确如此哦!

- Shell变量和数组使用详解

daizj

linuxshell变量数组

Shell 变量

定义变量时,变量名不加美元符号($,PHP语言中变量需要),如:

your_name="w3cschool.cc"

注意,变量名和等号之间不能有空格,这可能和你熟悉的所有编程语言都不一样。同时,变量名的命名须遵循如下规则:

首个字符必须为字母(a-z,A-Z)。

中间不能有空格,可以使用下划线(_)。

不能使用标点符号。

不能使用ba

- 编程中的一些概念,KISS、DRY、MVC、OOP、REST

dcj3sjt126com

REST

KISS、DRY、MVC、OOP、REST (1)KISS是指Keep It Simple,Stupid(摘自wikipedia),指设计时要坚持简约原则,避免不必要的复杂化。 (2)DRY是指Don't Repeat Yourself(摘自wikipedia),特指在程序设计以及计算中避免重复代码,因为这样会降低灵活性、简洁性,并且可能导致代码之间的矛盾。 (3)OOP 即Object-Orie

- [Android]设置Activity为全屏显示的两种方法

dcj3sjt126com

Activity

1. 方法1:AndroidManifest.xml 里,Activity的 android:theme 指定为" @android:style/Theme.NoTitleBar.Fullscreen" 示例: <application

- solrcloud 部署方式比较

eksliang

solrCloud

solrcloud 的部署其实有两种方式可选,那么我们在实践开发中应该怎样选择呢? 第一种:当启动solr服务器时,内嵌的启动一个Zookeeper服务器,然后将这些内嵌的Zookeeper服务器组成一个集群。 第二种:将Zookeeper服务器独立的配置一个集群,然后将solr交给Zookeeper进行管理

谈谈第一种:每启动一个solr服务器就内嵌的启动一个Zoo

- Java synchronized关键字详解

gqdy365

synchronized

转载自:http://www.cnblogs.com/mengdd/archive/2013/02/16/2913806.html

多线程的同步机制对资源进行加锁,使得在同一个时间,只有一个线程可以进行操作,同步用以解决多个线程同时访问时可能出现的问题。

同步机制可以使用synchronized关键字实现。

当synchronized关键字修饰一个方法的时候,该方法叫做同步方法。

当s

- js实现登录时记住用户名

hw1287789687

记住我记住密码cookie记住用户名记住账号

在页面中如何获取cookie值呢?

如果是JSP的话,可以通过servlet的对象request 获取cookie,可以

参考:http://hw1287789687.iteye.com/blog/2050040

如果要求登录页面是html呢?html页面中如何获取cookie呢?

直接上代码了

页面:loginInput.html

代码:

<!DOCTYPE html PUB

- 开发者必备的 Chrome 扩展

justjavac

chrome

Firebug:不用多介绍了吧https://chrome.google.com/webstore/detail/bmagokdooijbeehmkpknfglimnifench

ChromeSnifferPlus:Chrome 探测器,可以探测正在使用的开源软件或者 js 类库https://chrome.google.com/webstore/detail/chrome-sniffer-pl

- 算法机试题

李亚飞

java算法机试题

在面试机试时,遇到一个算法题,当时没能写出来,最后是同学帮忙解决的。

这道题大致意思是:输入一个数,比如4,。这时会输出:

&n

- 正确配置Linux系统ulimit值

字符串

ulimit

在Linux下面部 署应用的时候,有时候会遇上Socket/File: Can’t open so many files的问题;这个值也会影响服务器的最大并发数,其实Linux是有文件句柄限制的,而且Linux默认不是很高,一般都是1024,生产服务器用 其实很容易就达到这个数量。下面说的是,如何通过正解配置来改正这个系统默认值。因为这个问题是我配置Nginx+php5时遇到了,所以我将这篇归纳进

- hibernate调用返回游标的存储过程

Supanccy2013

javaDAOoracleHibernatejdbc

注:原创作品,转载请注明出处。

上篇博文介绍的是hibernate调用返回单值的存储过程,本片博文说的是hibernate调用返回游标的存储过程。

此此扁博文的存储过程的功能相当于是jdbc调用select 的作用。

1,创建oracle中的包,并在该包中创建的游标类型。

---创建oracle的程

- Spring 4.2新特性-更简单的Application Event

wiselyman

application

1.1 Application Event

Spring 4.1的写法请参考10点睛Spring4.1-Application Event

请对比10点睛Spring4.1-Application Event

使用一个@EventListener取代了实现ApplicationListener接口,使耦合度降低;

1.2 示例

包依赖

<p