计算机组成原理——总线控制(总线判优控制、总线通信控制)

总线控制

一、总线判优控制

1.基本概念:

总线判优控制的集中式方式有三种:链式查询、计数器定时查询、独立请求方式

1.链式查询方式

注:在查询链中离总线控制器最近的部件具有最高优先权,离总线控制器越远,优先权越低。

链式查询通过接口的优先权排队电路实现。

优点:结构简单,主要运用在简单的嵌入式系统中

缺点:速度慢,需要一直向下查询,对电路故障特别敏感

2.计数器定时查询方式:

注:计数器的初值可用程序设置,以方便地改变优先次序。当然这种灵活性是以增加控制线数为代价的。

如果计数器的初值是从0开始,各部件的优先次序与链式查询法相同。

如果从中止点开始,则每个设备使用总线的优先级相等。????这是为什么???

3.独立请求方式

注:优点:响应时间快,对优先次序的控制相当灵活 缺点:控制线数增加了很多

二、总线通信控制

同步通信

1、同步式数据输入

2、同步式数据输出

注:同步通信采用速度最慢的那个模块作为标准,即使有关模块的速度比较快,也要按照最慢的模块进行设置。

一般应用在总线长度比较短,并且各个模块的存取时间比较一致的情况下,使用同步式传输数据。

同步通信的优点:同步通信具有较高的传输效率,可靠性较高

缺点:所有模块都强求一致的同一时限,使设计缺乏灵活性。

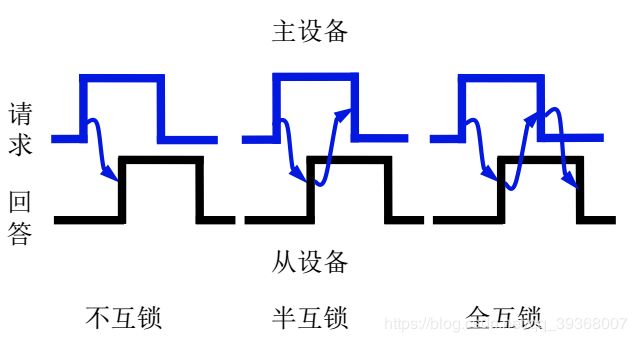

异步通信

半互锁的缺点:有可能导致“请求”信号一直保持高电平

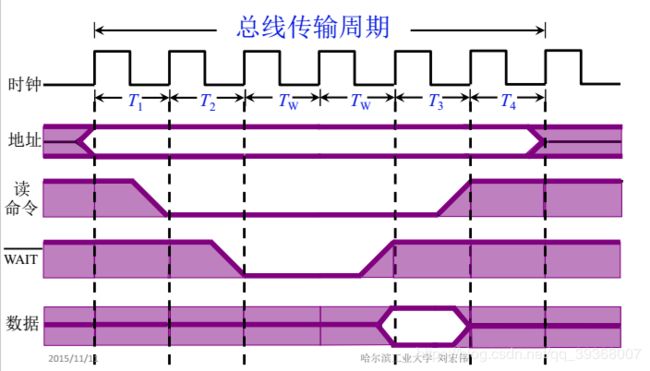

半同步通信(同步、异步相结合)

注:半同步通信适用于系统工作速度不高,但又包含了许多工作差异较大的各类设备的简单系统。

其控制方式比异步通信简单。

缺点:对系统时钟频率不能要求太高,故从整体上来看,系统工作的速度不会太高。

同步通信、异步通信、半同步通信,在整个传输周期中,系统总线的使用权完全由占有使用权的主模块和它选中的从模块占据。

分离式通信的两个子周期都只有单方向的信息流,每个模块都能充当一次主模块。

故:在分离式通信方式中,总线上所有模块都可以成为主模块。

1、计算机系统的五大部件之间两种互联方式为:总线连接和分散连接

2、相对于单总线结构,多总线结构解决了CPU、主存与I/O设备间速度不匹配的问题。

3、DMA总线用于主存与I/O设备之间交换信息

4、在同步通信中,一个总线周期的传输过程是先传输地址,再传输数据

5、所谓的三总线结构的计算机中的“三总线”包含:I/O总线 、主存总线、cpu总线

6、控制总线中常见的控制信号包括:总线请求、中断请求、传输响应

7、假设某系统总线在一个总线周期中并行传输8字节信息,一个总线周期占用4个时钟周期,总线时钟频率为10MHz,则总线带宽是:20MB/s

解析:1个时钟周期的时间为1/10MHz,每个时钟周期传输的字节数为8/4=2,则总线带宽为2/(1/10MHz)=20MB/s。

每个时钟周期传输的字节数 / 1个时钟周期的时间=总线带宽

8、总线的异步通信方式是不采用时钟信号,只采用握手信号;半同步通信方式是即采用时钟信号,又采用握手信号。

9、在异步串行传输系统中,假设每秒传输120个数据帧,其字符格式规定包含1个起始位,7个数据位,1个奇偶校验位,1个终止位,则波特率为:1200bps

解析:一帧包含1+7+1+1=10位 故波特率为10*120=1200bps 波特率=单位时间的数据帧数*帧位

10、按连接部件不同,总线通常可分为以下哪些种:片内总线、通信总线、系统总线