Quartus II和Modelsim的联合仿真(详细)

转自http://www.cnblogs.com/Jezze/archive/2012/09/14/2684333.html

这篇文章不需要在modelsim中建库、映射、建工程等一些繁琐的步骤,直接使用modelsim中的默认work库。使用quartus+modelsim联合仿真。

首先推荐一篇文章 http://www.cnblogs.com/emouse/archive/2012/07/08/2581223.html

首先,根据上一篇文章,建立一个testbench模板;

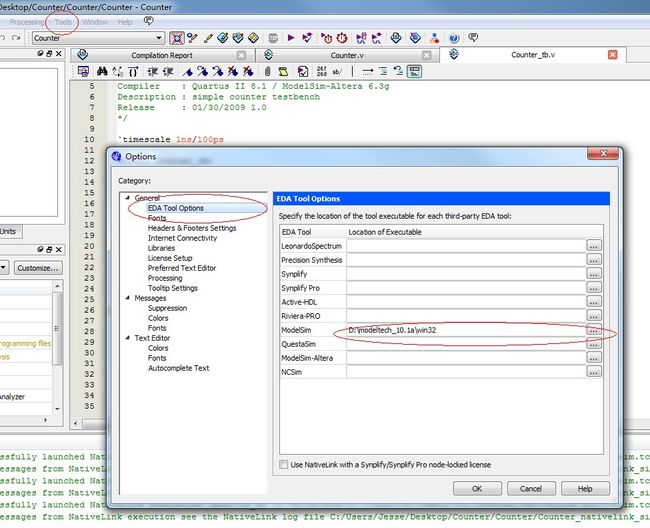

第一次用modelsim+quartus的时候需要在quartus中设置modelsim的路径,quartus->tools->general->EDA tool options ,在右边选择modelsim的安装路径,如下图:

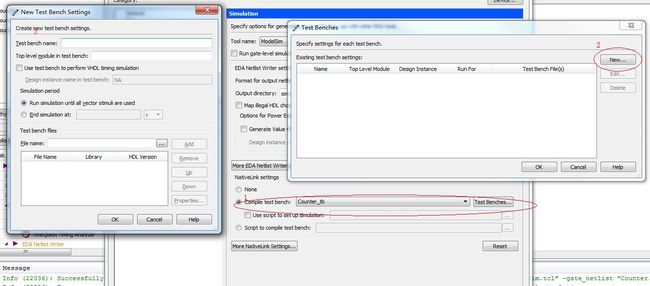

然后在Quartus->setting->simulation中设置仿真工具(选择modelsim),输出netlist语言(选择 VHDL or Verilog),然后在下面添加testbench;如下图:

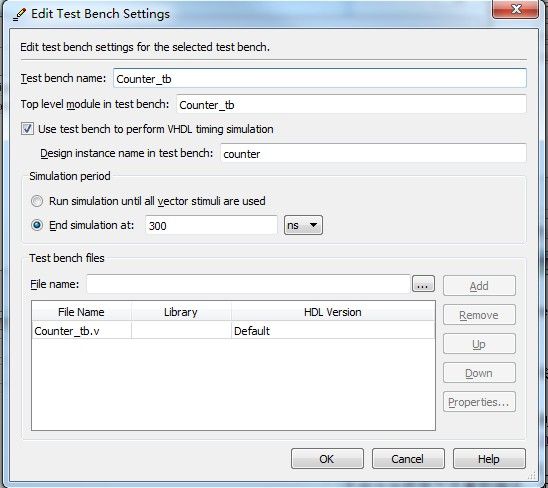

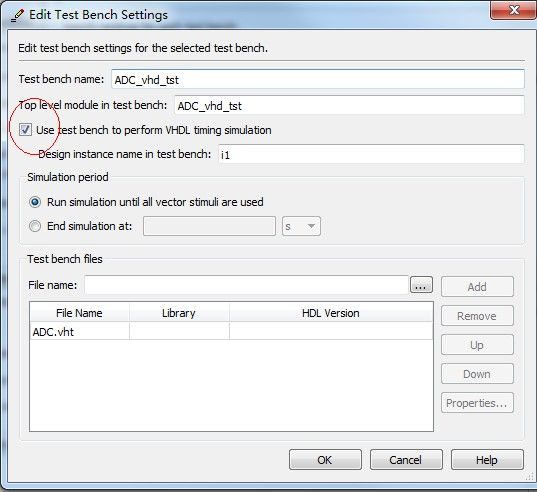

到edit test settings这个步骤的时候需要说明一下,其中test bench name可以自己定,下面两个的内容根据test bench文件中的内容而定。

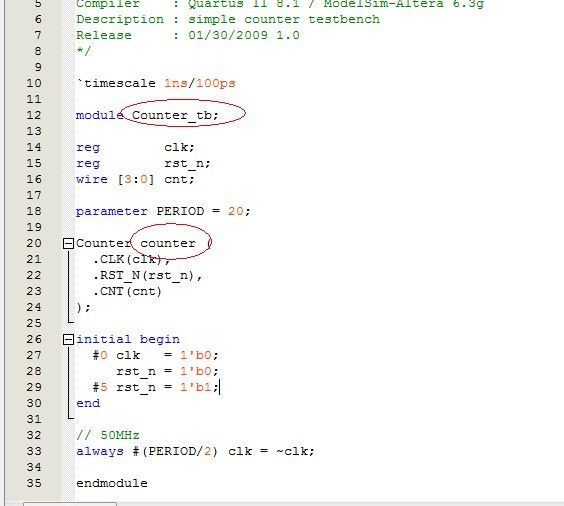

比如说我用verilog写的test bench如下:

那么我下面两个的名字就为分别为 Counter_tb和counter 如下图:

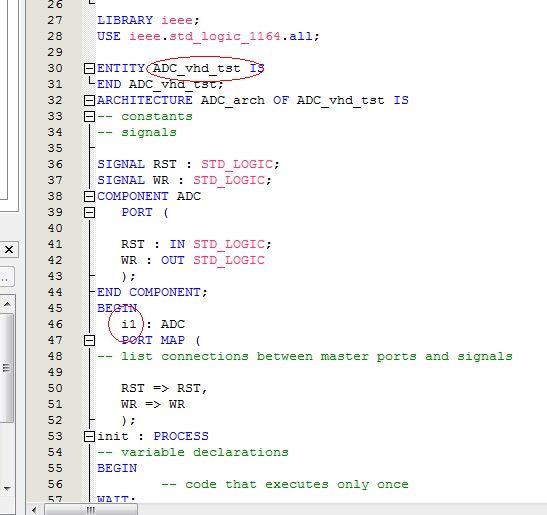

如果是用VHDL写的test bench,如下图

那么我们下面两个的内容就是ADC_vhd_tst和i1,如同下图

这样设置了之后,就可以从quartus中直接进行RTL仿真和门极(时序)仿真了,(上图打勾就代表使用时序仿真);具体为什么要这么设置请看http://www.uio.no/studier/emner/matnat/fys/FYS4220/h12/documentation/quartus_modelsim_setup.pdf 如果不这么设置的话,可以进行RTL仿真,但是不能进行门级(时序)仿真,门级(时序)仿真的时候会报 Failed to find INSTANCE 错误。

做到上一部可以编写程序,然后编译,接着运行RTL simulation,这个时候modelsim会自己启动,然后自己编译,接着在work library中会有两个单元,其中一个是testbench生成的,我们仿真的话是用这个。然后添加波形什么的就可以仿真了。

运行时序仿真的话单击quartus上的gate-level simulation按钮就可以了。

接着最关键的问题来了,如果我们修改了VHDL程序或者testbench,怎么在modelsim中更新,我在网上找了很多教程,发现只做到上一步就结束了,在modelsim中更新的话只有关掉modelsim,在quartus中重新进行RTL simulation,显然这样很麻烦,直到我看到这篇文章http://www.cnblogs.com/emouse/archive/2012/07/08/2581223.html,这边文章最后第7步完全可以不用做,我讲一下我的做法。

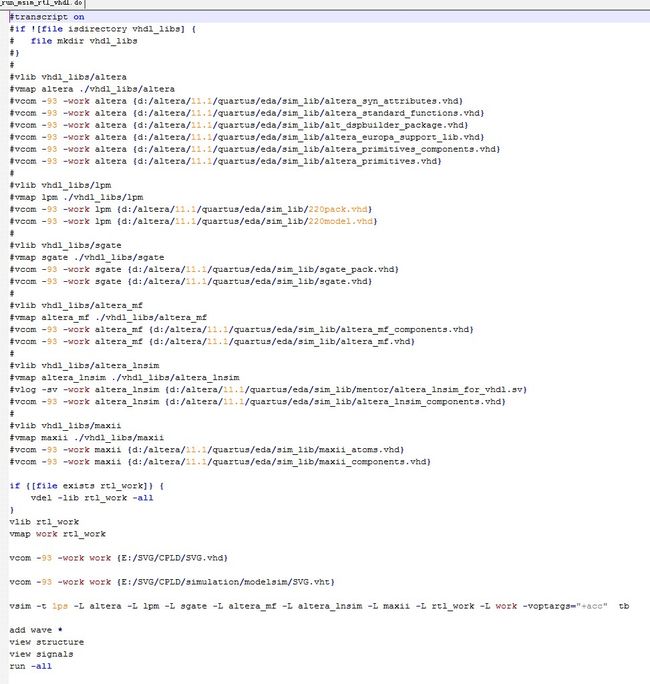

当运行RTL simulation的时候,modelsim会自己启动,且开始编译,这个是时候实际上它有个命令被输入了,你可以在transcripe中按向上的箭头,会发现有个do ****.do 的命令,你可以在simlation文件夹中找到这个do文件,如果你进行RTL仿真的话,会有****rtl****.do文件,亦然,如果进行gate-level 仿真的话,就有*******gate****.do 文件,请注意区分。当你修改了程序之后要想在modelsim中更新,直接敲这个do *****.do命令就OK了,但是每次敲这个命令会把库文件重新编译,大大浪费了时间,所以你可以找到这个文件,打开,把上面一部分编译库文件的指令注释掉,如下图:

这个时候执行do指令的话,几秒钟就执行完毕了,modelsim中也更新了。

当然modelsim中也可以不用test bench仿真,可以敲force指令生成波形,具体找资料吧。

在test bench中,输入信号都要初始化,否则会显示‘X’任意状态,且不能全都放在一个process中初始化,不然在别的process中对其操作也会呈现‘X’,最好要使用之前初始化一下就可以了.

好像RTL仿真修改了VHLD文件后不需要编译,直接使用do命令就可以更新仿真结果,门级仿真则需要编译一下,再使用do命令才会更新