VHDL(一):数据类型

1.预定义的数据类型

(1)std库的standard包集:定义了位(BIT)、布尔(Boolean)、整数(integer)和实数(real)数据类型。

(2)ieee库的std_logic_1164包集:定义了std_logic和std_ulogic数据类型。

(3)ieee库的std_logic_arith包集:定义了signed和unsigned数据类型。还定义了conv_integer(p),conv_unsigned(p,b)和conv_signed(p,b)和conv_std_logic_vector(p,b)等数据类型转换函数。

(4)ieee库的std_logic_signed和std_logic_unsigned包集:包含一些函数,这些函数可以使std_logic_vecture类型的数据进行

像signed和unsigned类型数据一样的运算。

(5)位(bit)和位矢量(bit_vector):位值用'0'或'1'表示。

例:

(a)signal x:bit;

--将x声明为一个位宽为1的bit类型的信号。

(b)signal y:bit_vector(3 downto 0);

--将y声明为一个位宽为4的位矢量,其中最左边的一位是最高位(MSB:most significant bit)。

(c)signal w:bit_vector(0 downto 7);

--将w声明为一个位宽为8的位矢量,它的最右边的一位是MSB。

(d)在定义了上述信号以后,可以采用下面的方式对信号赋值(必须使用"<="操作符给信号赋值)。

x<='1'; --x是位宽为1,值为'1'的信号。注意,当位宽为1时,位值放在单引号中。

y<="0111"; --y是位宽为4,值为"0111"(MSB='0')的信号。注意,当位宽大于1时,位矢量值放在双引号中。

w<="01111001" --w的位宽为8,值为"01111001"(MSB='1')的信号。

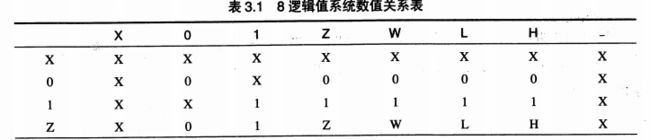

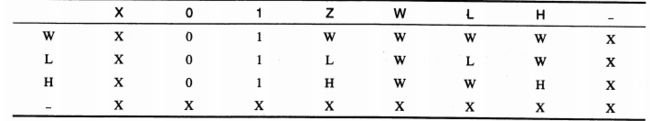

(6)std_logic和std_logic_vector:它们是ieee 1164标准中引入的8逻辑值系统。不同于bit 数据类型,它可以取'0','1',不定态和

高阻态等8种不同的值。

'X' “强” 不确定值(综合后为不确定值)

'0' “强” 0(综合后为0)

'1' “强” 1(综合后为1)

'Z' 高阻态(综合后为三态缓冲器)

'w' “弱” 不确定值

'L' “弱” 0

'H' “弱” 1

'-' 不可能出现的情况

例:

signal x:std_logic; --声明x是位宽为1的std_logic类型的信号。

signal y:std_logic_vector(3 downto 0) :="0001"; --声明y是一个位宽为4的矢量,其中最左边的一位是MSB。

对信号y赋初始值"0001"(可选)。

(7)std_ulogic和std_ulogic_vector:是ieee 1164标准中定义的具有9种逻辑值数据类型。std_logic类型是std_ulogic类型的一个子集。

后者引入了一个新的逻辑值'U',它代表初始不定值。与std_logic不同的是,std_ulogic中没有指定两个std_ulogic信号连接到同一个节点上发生冲突后的逻辑值,因此要避免两个输入信号进行直接连接。在确保两根输出线不会连接到一起的条件下,这种9个逻辑值系统可以用来检测设计时可能发生的错误。

布尔类型(boolean):只有两种取值,"真"或“假”。

整数(integer):32位的整数(取值范围从-2147483647到2147483647)

自然数(natural):非负的整数(从0到2147483647)

实数(real):实数的取值范围从-1x10^38到1x10^38,它是不可综合的。

物理量字符(physical literal)型:用来表示诸如时间和电压等物理量。在仿真时可以使用,但不可综合。

字符(character)型:可以是单个或者一串ASCII字符。

signed(有符号数)和unsigned(无符号数):它们是在ieee库std_logic_arith包集中定义的数据类型。

例:

x0<='0';--可以是bit,std_logic或者std_ulogic类型的值'0'

x1<='00011111'--可以是bit_vector,std_logic_vector,std_ulogic_vector,signed或unsigned类型的值。

x2<="0001_1111"--数字之间加下划线可以增加二进制的可读性

x3<="101111"--二进制数"101111",表示十进制47

x4<=B"101111";--二进制数"101111",表示十进制47

x5<=O"57"

y<=1.2E-5; --实数,不可以综合

q<=d after 10 ns;--物理量,不可综合

例:

(8)不同类型数据之间的合法与非法操作:

signal a:bit;

signal b:bit_vector(7 downto 0);

signal c:std_logic;

signal d:std_logic_vector(7 downto 0);

signal e: integer range 0 to 255;

……

a<=b(5);--合法(标量类型:bit)

b(0)<=a;--合法(标量类型:bit)

c<=d(5);--合法(标量类型:std_logic)

d(0)<=c;--合法(标量类型:std_logic)

a<=c;--非法(bit和std_logic数据类型不匹配)

b<=d;--非法(bit_vector和std_logic_vector数据类型不匹配)

e<=b;--非法(integer和bit_vector数据类型不匹配)

e<=d;--非法(integer和std_logic_vector数据类型不匹配)

2.VHDL自定义数据类型

用户自定义的数据类型:integer(整数)和enumerated(枚举)。

(1)用户定义的整数(integer)类型:

TYPE integer is range -2147483647 to +2147483647; --用户定义的整数类型,与预定义的整数类型是相同的。

TYPE natural is range 0 to +2147483647; --用户定义的自然数类型,与预定义的自然数类型是相同的。

TYPE my_integer is range -32 to 32; --用户定义的整数类型的子集。

TYPE student_grade is range -32 to 32; --用户定义的自然数类型的子集。

(2)用户定义的枚举(enumerated)类型:

TYPE BIT IS('0','1'); --与预定义的bit数据类型在本质上是相同的。

TYPE my_logic is('0','1','z'); --用户定义的std_logic类型的子集。

type bit_vector is array(natural range< >) of bit; --用户定义的bit_vector数据类型。

(3)--range< >表示数据取值范围没有约束。

(4)--natural range< >表示数据约束在自然数范围内。

TYPE state is(idle,forward,backward,stop); --枚举数据类型,常用于有限机的定义。

TYPE color is (red,green,blue,white); --另一种枚举类型的定义。

一般来说,枚举类型的数据自动按顺序依次编码。

转载:https://www.cnblogs.com/lhkhhk/p/11845169.html