计算机组成与系统结构(课程设计)

一、本课程设计的性质、目的、任务

《计算机组成与系统结构课程设计》是计算机学院各专业集中实践性环节之一,是学习完《计算机组成与系统结构》课程后进行的一次全面的综合练习。其目的是综合运用所学计算机原理知识,设计并实现一台模型计算机,以便巩固所学的知识,提高分析问题和解决问题的能力。

二、本课程设计的基本理论

1、掌握算术、逻辑、移位运算实验,熟悉ALU运算控制位的运用。

2、掌握存储器组织、读写方式及与总路线组成的数据通路,掌握地址总线、数据总线的工作原理。

3、掌握指令结构和指令取指、执行工作过程。

4、掌握CPU的微程序控制原理。

三、题目

1、综合运用所学计算机原理知识,设计并实现具有以下指令集结构的模型计算机:

| 编号 |

助记符 |

机器指令码 |

说明 |

| 1 |

IN Rd,IOL |

0001Rd00 |

i/o(数据开关)低字节→RS |

| 2 |

OUT IOH,Rs |

001000Rs |

Rs→i/o(数据开关)高字节 |

| 3 |

LDA Rd,M |

0011Rd00 XXXXXXXX XXXXXXXX |

[M] →RD |

| 4 |

STA M,Rs |

010000Rs XXXXXXXX XXXXXXXX |

Rs→[M] |

| 5 |

ADD Rd,Rs |

0101RdRs |

Rd+Rs→Rd |

| 6 |

SUB Rd,Rs |

0110RdRs |

Rd-Rs→Rd |

| 7 |

RL Rd |

0111Rd00 |

Rd循环左移一位 |

| 8 |

RR Rd |

1000Rd00 |

Rd循环右移一位 |

| 9 |

MOV Rd,Rs |

1001RdRs |

Rs→Rd |

| 10 |

JMP M |

10100000 XXXXXXXX XXXXXXXX |

[M]→PC,即跳转到M所指单元 |

| 11 |

JZ M |

10110000 XXXXXXXX XXXXXXXX |

当Z=1时,跳转到M所指单元 |

| 12 |

JC M |

11000000 XXXXXXXX XXXXXXXX |

当CY=1时,跳转到M所指单元 |

| 13 |

CLR Rd |

1101Rd00 |

将Rd清零 |

| 14 |

DEC Rd |

1110Rd00 |

将Rd值减1 |

| 15 |

HALT |

11110000 |

停机 |

其中,高4位为指令操作码,M为16位存储器地址, Rs为源寄存器,Rd为目的寄存器,占2位,并规定:

| Rs或Rd |

选定的寄存器 |

| 00 01 10 11 |

R0 R1 R2 R3 |

2、利用上述指令集编写汇编程序,并在所设计的模型计算机上调试通过:

用累加的方法实现字节乘法(不溢出情况),被乘数:R0,乘数:R1,积:R2并输出至I/O。

- 数据格式定义

- 数据格式

模型机规定采用定点补码表示数据,且字长为8位,其格式如下:

| 7 |

6 5 4 3 2 1 0 |

| 符号 |

尾 数 |

其中第7位为符号位,数值表示范围是:-1≤X<1。

- 指令格式

模型机设计四大类指令共16条,其中包括算术逻辑指令、I/O指令、访问及转移指令和停机指令。

⑴ 算术逻辑指令

设计9条算术逻辑指令并用单字节表示,寻址方式采用寄存器直接寻址,其格式如下:

| 7 6 5 4 |

3 2 |

1 0 |

| OP-CODE |

Rs |

Rd |

其中,OP-CODE为操作码,Rs为源寄存器,Rd为目的寄存器,并规定:

| Rs或Rd |

选定的寄存器 |

| 00 01 10 11 |

R0 R1 R2 R3 |

9条算术逻辑指令的名称、功能和具体格式见表7-12-1。

⑵ 访问指令及转移指令

模型机设计2条访问指令,即存数(STA)、取数(LDA),2条转移指令,即无条件转移(JMP)、结果为零或有进

位转移指令(BZC),指令格式为:

| 7 |

6 |

5 4 |

3 2 |

1 0 |

| 0 |

0 |

M |

2OP-CODE |

Rd |

| D(低八) |

||||

| D(高八) |

||||

其中“0 0 M ”为源码段,2OP-CODE为目的码段(LDA、STA指令使用)。D为十六位地址段(低八在前,高八随后),M为源寻址模式,其定义如下:

| 寻址模式M |

有效地址E |

说 明 |

| 00 01 10 11 |

E = D E = (D) E = (SP)+D E = (PC)+D |

直接寻址 间接寻址 SP变址寻址 相对寻址 |

⑶ I/O指令

输入(IN)和输出(OUT)指令采用单字节指令,其格式如下:

| 7 6 5 4 |

3 2 |

1 0 |

| OP-CODE |

0 0 |

Rd |

⑷ 停机指令

指令格式如下:

| 7 6 5 4 |

3 2 |

1 0 |

| OP-CODE |

0 0 |

0 0 |

HALT指令,用于实现停机操作。

五、模型机指令系统(用列表方式给出,含助记符、操作数、指令码、长度、注释等)

1.微程序:

| 编号 |

助记符 |

机器指令码 |

说明 |

微程序入口地址 |

微程序 |

| 1 |

IN Rd,IOL |

0001Rd00 |

i/o(数据开关)低字节→rs |

620 |

620:F0 FC 6D |

| 2 |

OUT IOH,Rs |

001000Rs |

Rs→i/o(数据开关)高字节 |

640 |

640:F5 F9 ED |

| 3 |

LDA Rd,M |

0011Rd00 XXXXXXXX XXXXXXXX |

[M] →RD |

660 |

660:FA FB 7F 661:BB FB FF 662:BC C6 3F 663:70 FB ED |

| 4 |

STA M,Rs |

010000Rs XXXXXXXX XXXXXXXX |

Rs→[M] |

680 |

680:FA FB 7F 681:BB FB FF 682:BC C6 3F 683:5F F9 ED |

| 5 |

ADD Rd,Rs |

0101RdRs |

Rd+Rs→Rd |

6A0 |

6A0:F8 F9 7F 6A1:FA F9 FF 6A2:F0 66 6D |

| 6 |

SUB Rd,Rs |

0110RdRs |

Rd-Rs→Rd |

6C0 |

6C0:F8 F9 7F 6C1:FA F9 FF 6C2:F0 6E 6D |

| 7 |

RL Rd |

0111Rd00 |

Rd循环左移一位 |

6E0 |

6E0:F8 F9 7F 6E1:F0 76 6D |

| 8 |

RR Rd |

1000Rd00 |

Rd循环右移一位 |

700 |

700:F8 F9 7F 701:F0 7E 6D |

| 9 |

MOV Rd,Rs |

1001RdRs |

Rs→Rd |

720 |

720:F0 F9 ED |

| 10 |

JMP M |

10100000 XXXXXXXX XXXXXXXX |

[M]→PC,即跳转到M所指单元 |

740 |

740:FA FB FF 741:BB FB FF 742:3F C6 2D |

| 11 |

JZ M |

10110000 XXXXXXXX XXXXXXXX |

当Z=1时,跳转到M所指单元 |

760 |

760:FA FB FF 761:BB FB FF 762:BC C6 3C 764:FF FF ED 765:3F C6 2D |

| 12 |

JC M |

11000000 XXXXXXXX XXXXXXXX |

当CY=1时,跳转到M所指单元 |

780 |

780:FA FB FF 781:BB FB FF 782:BC C6 3D 784:FF FF ED 785:3F C6 2D |

| 13 |

CLR Rd |

1101Rd00 |

将Rd清零 |

7A0 |

7A0:F0 DE 4D |

| 14 |

DEC Rd |

1110Rd00 |

将Rd值减1 |

7C0 |

7C0:F8 F9 5F 7C1:F0 D6 4D |

| 15 |

HALT |

11110000 |

停机 |

7E0 |

7E0:F8 F8 DF 7E1:3F D6 0D |

2.指令系统:

;基本模型机指令系统

;助记符 操作数 指令码 长度 解释

;---------------------------------------------------------------------------------------------------------------------------

IN R0,IOL 10 1 ;IOL->R0

IN R1,IOL 14 1 ;IOL->R1

IN R2,IOL 18 1 ;IOL->R2

IN R3,IOL 1C 1 ;IOL->R3

OUT IOH,R0 20 1 ;R0->IOH

OUT IOH,R1 21 1 ;R1->IOH

OUT IOH,R2 22 1 ;R2->IOH

OUT IOH,R3 23 1 ;R3->IOH

LDA R0,* 30 3 ;[addr]->R0

LDA R1,* 34 3 ;[addr]->R1

LDA R2,* 38 3 ;[addr]->R2

LDA R3,* 3C 3 ;[addr]->R3

STA *,R0 40 3 ;R0->[addr]

STA *,R1 41 3 ;R1->[addr]

STA *,R2 42 3 ;R2->[addr]

STA *,R3 43 3 ;R3->[addr]

ADD R0,R0 50 1 ;R0+R0->R0

ADD R0,R1 51 1 ;R0+R1->R0

ADD R0,R2 52 1 ;R0+R2->R0

ADD R0,R3 53 1 ;R0+R3->R0

ADD R1,R0 54 1 ;R1+R0->R1

ADD R1,R1 55 1 ;R1+R1->R1

ADD R1,R2 56 1 ;R1+R2->R1

ADD R1,R3 57 1 ;R1+R3->R1

ADD R2,R0 58 1 ;R2+R0->R2

ADD R2,R1 59 1 ;R2+R1->R2

ADD R2,R2 5A 1 ;R2+R2->R2

ADD R2,R3 5B 1 ;R2+R3->R2

ADD R3,R0 5C 1 ;R3+R0->R3

ADD R3,R1 5D 1 ;R3+R1->R3

ADD R3,R2 5E 1 ;R3+R2->R3

ADD R3,R3 5F 1 ;R3+R3->R3

SUB R0,R0 60 1 ;R0-R0->R0

SUB R0,R1 61 1 ;R0-R1->R0

SUB R0,R2 62 1 ;R0-R2->R0

SUB R0,R3 63 1 ;R0-R3->R0

SUB R1,R0 64 1 ;R1-R0->R1

SUB R1,R1 65 1 ;R1-R1->R1

SUB R1,R2 66 1 ;R1-R2->R1

SUB R1,R3 67 1 ;R1-R3->R1

SUB R2,R0 68 1 ;R2-R0->R2

SUB R2,R1 69 1 ;R2-R1->R2

SUB R2,R2 6A 1 ;R2-R2->R2

SUB R2,R3 6B 1 ;R2-R3->R2

SUB R3,R0 6C 1 ;R3-R0->R3

SUB R3,R1 6D 1 ;R3-R1->R3

SUB R3,R2 6E 1 ;R3-R2->R3

SUB R3,R3 6F 1 ;R3-R3->R3

RL R0 70 1 ;R0循环左移一位

RL R1 74 1 ;R1循环左移一位

RL R2 78 1 ;R2循环左移一位

RL R3 7C 1 ;R3循环左移一位

RR R0 80 1 ;R0循环右移一位

RR R1 84 1 ;R1循环右移一位

RR R2 88 1 ;R2循环右移一位

RR R3 8C 1 ;R3循环右移一位

MOV R0,R0 90 1 ;R0->R0

MOV R0,R1 91 1 ;R1->R0

MOV R0,R2 92 1 ;R2->R0

MOV R0,R3 93 1 ;R3->R0

MOV R1,R0 94 1 ;R0->R1

MOV R1,R1 95 1 ;R1->R1

MOV R1,R2 96 1 ;R2->R1

MOV R1,R3 97 1 ;R3->R1

MOV R2,R0 98 1 ;R0->R2

MOV R2,R1 99 1 ;R1->R2

MOV R2,R2 9A 1 ;R2->R2

MOV R2,R3 9B 1 ;R3->R2

MOV R3,R0 9C 1 ;R0->R3

MOV R3,R1 9D 1 ;R1->R3

MOV R3,R2 9E 1 ;R2->R3

MOV R3,R3 9F 1 ;R3->R3

JMP * A0 3 ;无条件转移到[addr]

JZ * B0 3 ;当Z=1时,跳转到[addr]所指单元

JC * C0 3;当CY=1时,跳转到M所指单元

CLR R0 D0 1 ;将R0清零

CLR R1 D4 1 ;将R1清零

CLR R2 D8 1 ;将R2清零

CLR R3 DC 1 ;将R3清零

DEC R0 E0 1 ;将R0值减1

DEC R1 E4 1 ;将R1值减1

DEC R2 E8 1 ;将R2值减1

DEC R3 EC 1 ;将R3值减1

HALT "" F0 1 ;停机

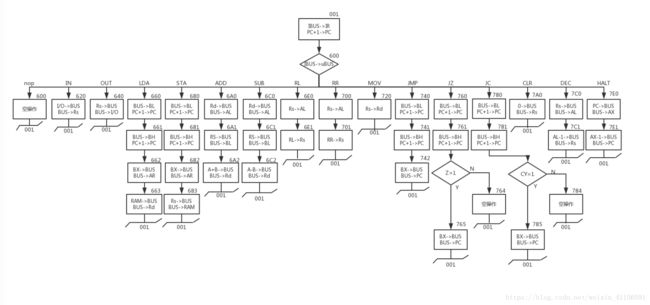

3.指令流程图

4.微指令表

| 微址 |

M23 |

M22 |

M21 |

M20 |

M19 |

M18 |

M17 |

M16 |

代码 |

M15 |

M14 |

M13 |

M12 |

M11 |

M10 |

M9 |

M8 |

代码 |

M7 |

M6 |

M5 |

M4 |

M3 |

M2 |

M1 |

M0 |

代码 |

后续微址 |

说明 |

| E/M |

IP |

MWR |

R/M |

o2 |

o1 |

o0 |

OP |

M |

CN |

S2 |

S2 |

S0 |

X2 |

X1 |

X0 |

XP |

W |

ALU |

Iu |

IE |

IR |

Icz |

Ids |

||||||

| 000 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

FF |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

FF |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

FF |

+1 |

空操作 |

| 001 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

BF |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

FB |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

F8 |

可变 |

ibus→ir |

| 620 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

F0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

FC |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

6D |

001 |

i/o→RD |

| 640 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

F5 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

F9 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

ED |

001 |

RS->i/o |

| 660 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

FA |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

FB |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

7F |

+1 |

RAM→Bl |

| 661 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

BB |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

FB |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

FF |

+1 |

RAM→BH |

| 662 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

BC |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

C6 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

3F |

+1 |

BX->aR |

| 663 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

70 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

FB |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

ED |

001 |

RAM->RD |

| 680 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

FA |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

FB |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

7F |

+1 |

RAM→Bl |

| 681 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

BB |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

FB |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

FF |

+1 |

RAM→BH |

| 682 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

BC |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

C6 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

3F |

+1 |

BX->aR |

| 683 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

5F |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

F9 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

ED |

001 |

RD->RAM |

| 6A0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

F8 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

F9 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

7F |

+1 |

RD->AL |

| 6A1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

FA |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

F9 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

FF |

+1 |

RS->BL |

| 6A2 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

F0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

66 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

6D |

001 |

AL+Bl->RD |

| 6C0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

F8 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

F9 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

7F |

+1 |

RD->AL |

| 6C1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

FA |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

F9 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

FF |

+1 |

RS->BL |

| 6C2 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

F0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

6E |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

6D |

001 |

AL-Bl->RD |

| 6E0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

F8 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

F9 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

7F |

+1 |

Rd->AL |

| 6E1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

F0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

76 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

6D |

001 |

RL->Rd |

| 700 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

F8 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

F9 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

7F |

+1 |

Rd->AL |

| 701 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

F0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

7E |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

6D |

001 |

RR->Rd |

| 720 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

F0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

F9 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

ED |

001 |

RS->RD |

| 740 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

FA |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

FB |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

FF |

+1 |

RAM→Bl |

| 741 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

BB |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

FB |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

FF |

+1 |

RAM→BH |

| 742 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

3F |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

C6 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

2D |

001 |

BX->PC |

| 760 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

FA |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

FB |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

FF |

+1 |

RAM→Bl |

| 761 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

BB |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

FB |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

FF |

+1 |

RAM→BH |

| 762 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

BC |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

C6 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

3C |

764 |

条件变址 |

| 764 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

FF |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

FF |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

ED |

001 |

空操作 |

| 765 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

3F |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

C6 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

2D |

001 |

BX->PC |

| 780 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

FA |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

FB |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

FF |

+1 |

RAM→Bl |

| 781 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

BB |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

FB |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

FF |

+1 |

RAM→BH |

| 782 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

BC |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

C6 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

3D |

784 |

条件变址 |

| 784 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

FF |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

FF |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

ed |

001 |

空操作 |

| 785 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

3F |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

C6 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

2D |

001 |

BX->PC |

| 7A0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

F0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

DE |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

4D |

001 |

0->RS |

| 7C0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

F8 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

F9 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

5F |

+1 |

RS->AL |

| 7C1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

F0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

D6 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

4D |

001 |

A-1->RS |

| 7E0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

F8 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

F8 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

DF |

+1 |

PC->AX |

| 7E1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

3F |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

D6 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0D |

001 |

A-1->PC |