杂谈『内存(RAM)简单存储原理』

前言

内存芯片最底层就是无数个开关,什么样的原理?它可以保存数据,为什么一旦断电会丢失所有数据(多少人悔青了肠子=.=),本文就从一个个的开关开始探讨..

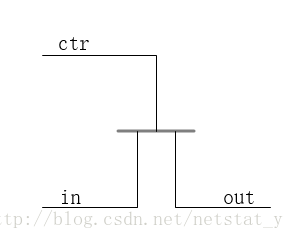

1.一个可以做开关的晶体管

这个晶体管内部,两个导体加一个半导体的材料隔开。关于半导体,只要初中物理不是音乐老师教的应该都知道。1

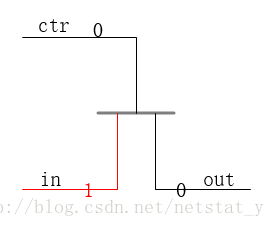

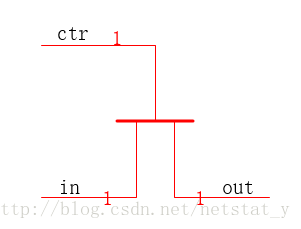

它有一个控制端(ctr),一个输入端(in),一个输出端(out)

控制端(ctr)充当一个开关的作用:

当(in)输入电流时, (ctr)不输入电流,这是一个断开的状态,(out)为 0。(以有电为1,无电为0)

2.电路逻辑

为了方便理解,我们把电信号转为布尔代数,true(电信号1),false(电信号0),把它抽象出一层,组成电路逻辑单元。

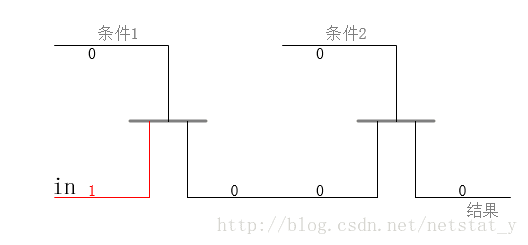

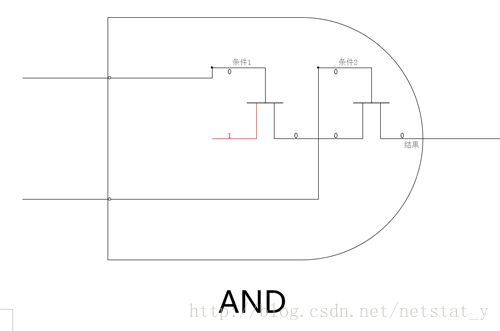

2.1 与门(AND)

仅当输入均为高电压(1)时,输出才为高电压(1)时2(在CSDN..应该都不用多解释)

电路结构:

非常简单,需要用到两个晶体管,第一个的(out)接入第二个的(in),如图

条件1和条件2,任何一个为false, 其最后结果处都是false。

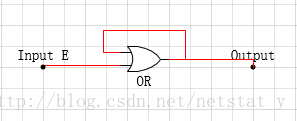

2.2 或门(OR)

只要两个输入中至少有一个为高电平(1),则输出为高电平(1);若两个输入均为低电平(0),输出才为低电平(0)。3

电路结构:

使用两个晶体管,并联(in) 端与(out)端,如图

条件1和条件2,任何一个为true, 其最后结果处都是true。

例,条件1 = true, 条件2 = false

同样,封装一下,用这样的一个符号表示它。

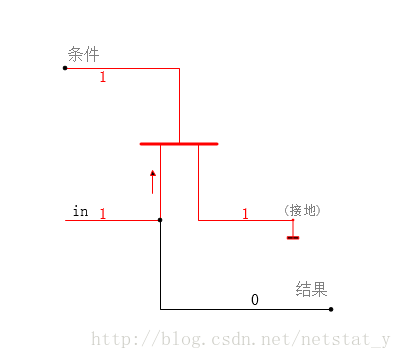

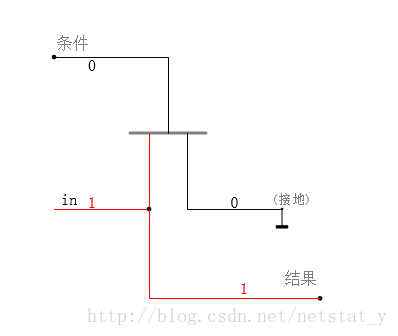

2.3 非门(NOT)

也叫反相器,与输入的刚好相反,输入高电平(1),则输出为低电平(0);输入低电平(0),则输出为高电平(1)。

电路结构:

只需要一个晶体管,但是它有点特殊,需要接地;默认的,条件false,它的结果是true。如图

一旦接地,(in)端的电流会喜欢更好更易通过的接地线路,而结果端会输出 false(0)。

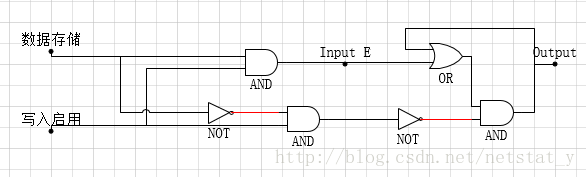

3. 储存 1bit

一瞬间它会回到另一个Inuput 接口,之后 Inuput E 无论如何操作 Output 都不会改变。

( •̀ ω •́ )✧ 终于有一个可以存储1bit 的电路逻辑了!

到这里你应该已经明白了,为什么断电会丢失数据;它没有任何物理标记,依赖于持续的电流保存记录,一旦断电所有数据为(0),即使再次恢复电流,也找不回当初的状态。

3.1 改进

现在有两个输入端 Input E 和 Input F;

如果我需要存储一个高电平(1)的bit, 在 Input E 端输入一个高电平信号。

如果我需要存储一个低电平(0)的bit, 在 Input E 端输入一个低电平信号(0), 在 Input F 端输入一个高电平信号(1)。

可是这仍然不够好,存储一个低电平(0)的bit,需要两个输入,而且还不好理解,下图更完美,[]~( ̄▽ ̄)~*

真正的内存远没有那么简单,要把它们组合成大空间,线路需要多路复用,内存地址,更好的电路逻辑门。

可能会写一篇关于内存地址的博文,wait..

- 半导体是指一种导电性可受控制,范围可从绝缘体至导体之间的材料。 ↩

- 与门 -维基百科 ↩

- 或门 - 维基百科 ↩