Verilog:generate、for、always 语句用法与电路结构对比

文章目录

-

- 1、always-for

- 2、 for-always

- 3、generate_for_always

- 3.1、generate-always-for

- 4、for-assign

- 5、generate-for-assign

- 6、always@(*)-for

- 7、for-always@(*)

- 8、generate_for_always@(*)

- 仿真结果

最近写Verilog时,对于generate-for 和 for循环相关不是很清楚,所以写了一些代码对比一下不同写法的结果,记录一下,如有错误请多多指正,不喜轻喷。

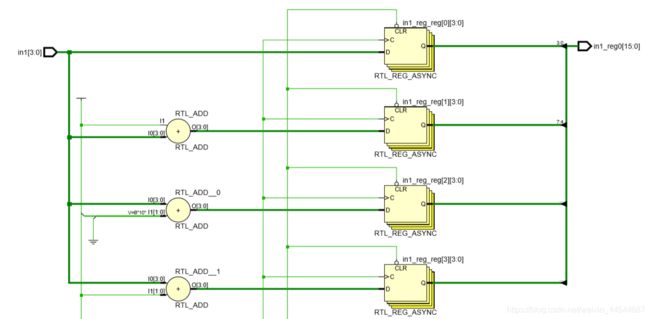

1、always-for

代码:

reg [data_width-1:0] in1_reg [0:depth-1];

integer i;

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

begin

for(i=0;i仿真结果说明:in1_reg 在第一个有效时钟沿后,数据均变为目标值

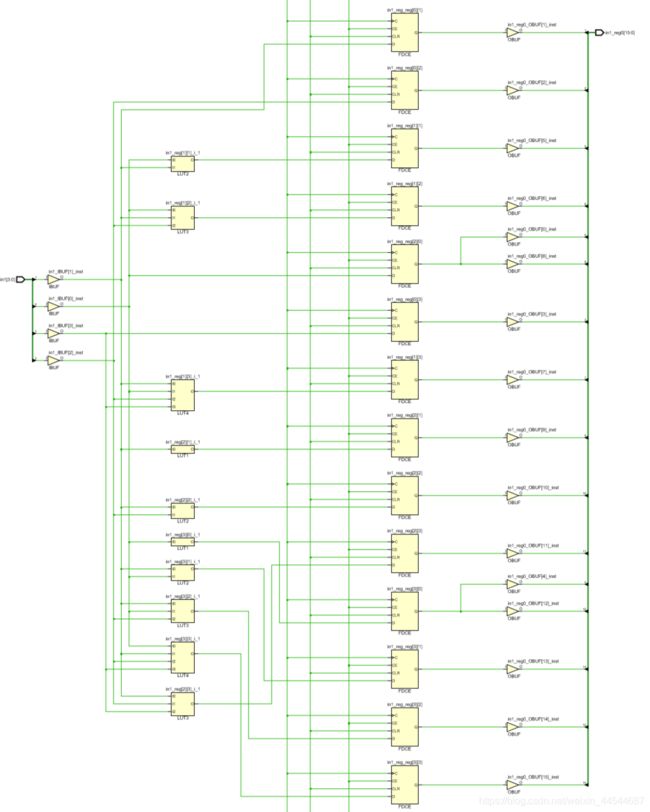

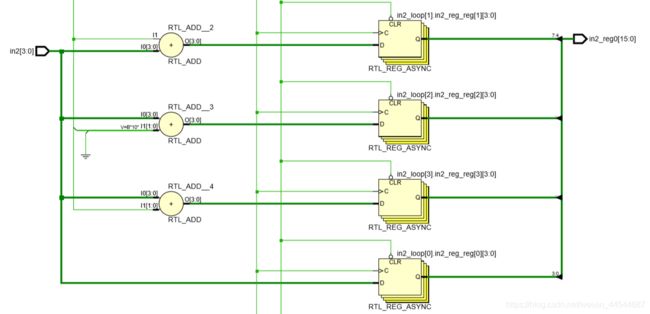

2、 for-always

代码:

//integer j; // Error:j is not a genvar;j is not a constant

genvar j;

reg [data_width-1:0] in2_reg [0:depth-1];

for(j=0;j仿真结果说明:in2_reg 在第一个有效时钟沿后,数据均变为目标值

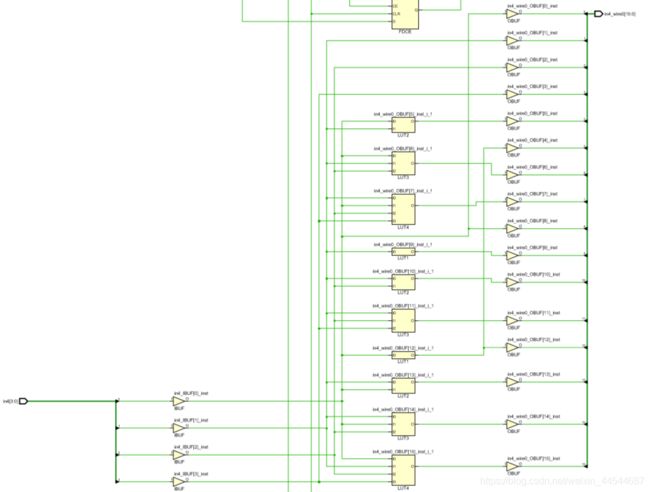

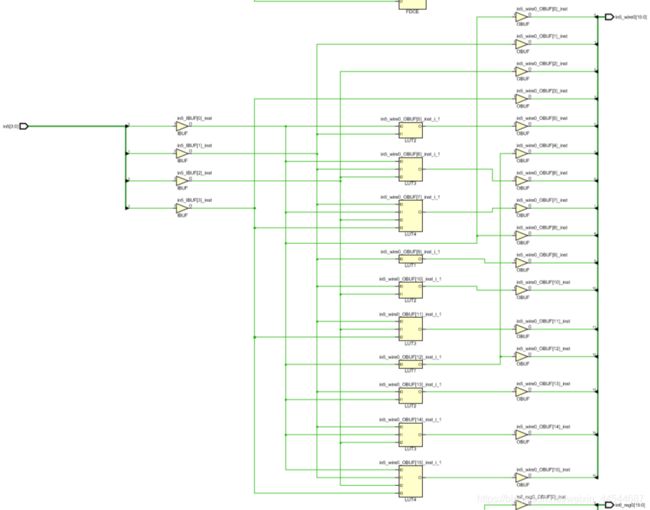

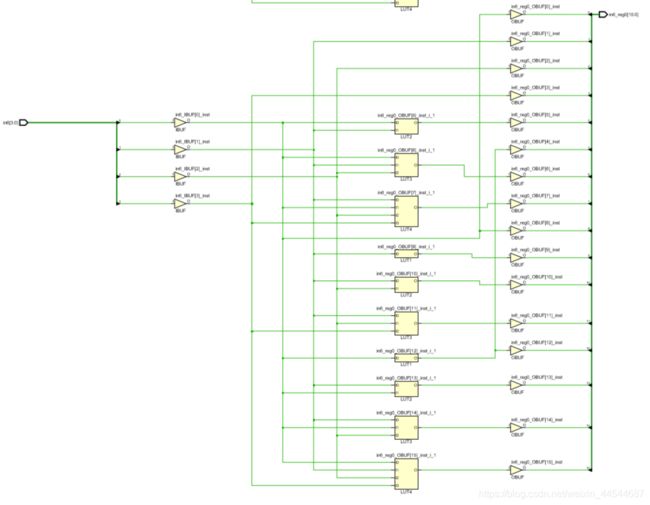

ANALYSIS得到的结构图

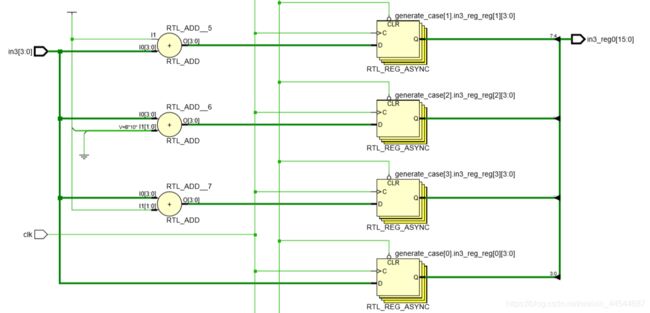

3、generate_for_always

代码:

reg [data_width-1:0] in3_reg [0:depth-1];

genvar k;

generate

for(k=0;k仿真结果说明:in3_reg 在第一个有效时钟沿后,数据均变为目标值

3.1、generate-always-for

代码:

reg [data_width-1:0] in31_reg [0:depth-1];

//genvar k1; // Error:procedural assignment to a non-register k1 is not permitted, left-hand side should be reg/integer/time/genvar

integer k1;

generate

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

begin

for(k1=0;k1仿真结果说明:in31_reg 在第一个有效时钟沿后,数据均变为目标值

4、for-assign

代码:

wire[data_width-1:0] in4_wire [0:depth-1];

//integer n; // Error: n is not a genvar;n is not a constant

genvar n;

for(n=0;n仿真结果说明:wire型,仿真开始即有值,随输入信号变化而变化

5、generate-for-assign

代码:

wire[data_width-1:0] in5_wire [0:depth-1];

genvar m;

generate

for(m=0;m仿真结果说明:wire型,仿真开始即有值,随输入信号变化而变化

6、always@(*)-for

代码:

reg [data_width-1:0] in6_reg [0:depth-1];

always@(*)

begin

for(i=0;i仿真结果说明:wire型,仿真开始即有值,随输入信号变化而变化

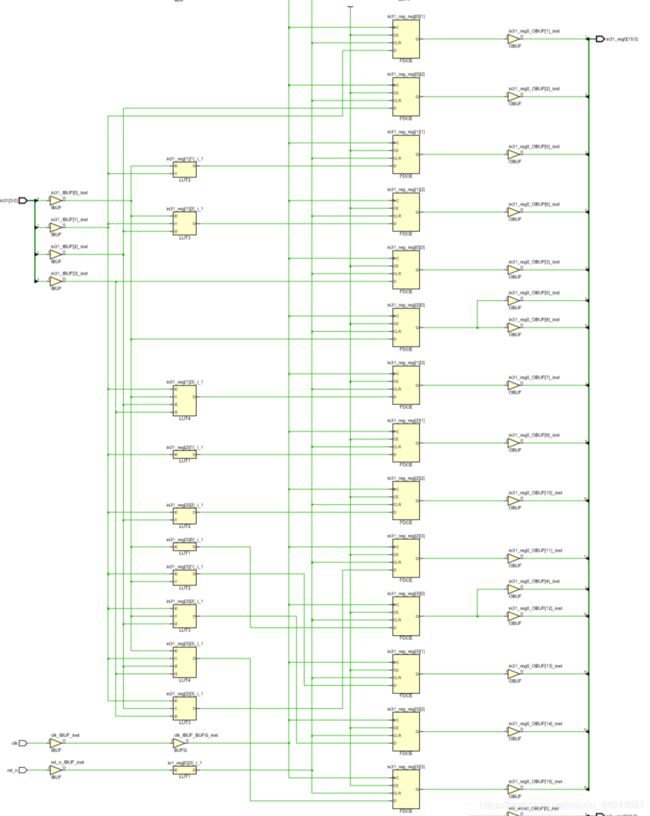

7、for-always@(*)

可以用 for-assign 替换

8、generate_for_always@(*)

可以用generate-assign 替换

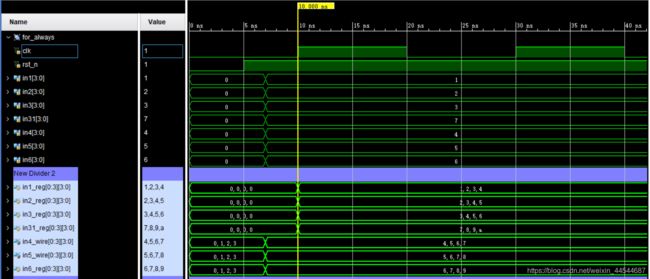

仿真结果

可以看到,时序信号in1_reg,in2_reg,in3_reg,in31_reg 都在第一个有效时钟边沿后变为目标值;组合逻辑信号in4_wire, in5_wire, in6_reg 在电路开始仿真时即被赋值进行运算,输入数据变化后随之发生变化

2、根据电路结构,generate-for 和 for 循环对于always 和 assig 语句的作用相同,但书写方法不同

generate-for / for循环在alway块外面时,循环变量要定义为 genvar 型

for 循环在always 块内时,循环遍历要定义为 integer 类型

3、结论:

若要在循环/条件/分支语句中调用模块,须使用 generate-for语句,注意要用genvar 定义循环变量,并在for循环的 begin: 后跟上 循环名称;

其他情况可根据自身情况而定

generate-for和for循环使用说明可见 Verilog:generate-for 语句(用法,及与for语句区别)

文中的代码等可见https://download.csdn.net/download/weixin_44544687/13117406