2023年第三届HiPChips解读

(The 3rd International Workshop on High Performance Chiplet and Interconnect Architectures (HiPChips) )[https://hipchips.github.io/isca2023/#schedule]

主题

Architecture

- Chiplet-enabled architectures with emerging technologies (e.g., in-memory computing, optical computing, quantum computing, etc)

- Hardware software co-designs for chiplet architecture

- High performance computing architectures enabled by fast interconnect

- Power and performance modeling for chiplet architectures

Interconnect

- Interconnect technologies for coherent and non-coherent data sharing

- Emerging on-chip interconnect for large-scale heterogeneous computing

- Novel software optimizations and scheduling with inter-chiplet network

议题

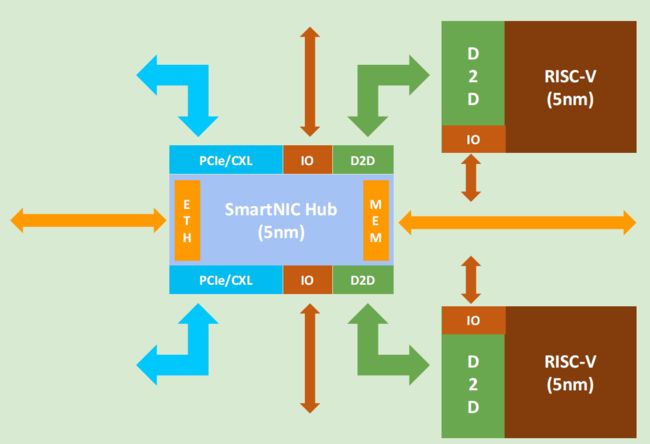

A chiplet based SmartNIC Platform using BoW

使用BoW的chiplet技术的SmartNIC平台。简单提到chiplet技术可利用与SmartNIC平台,讲了设计时的注意点,并宣传了chiplet生态,总体表现了对Chiplet技术的畅想。

Speaker: Suresh Subramaniam (Apex Confidential)

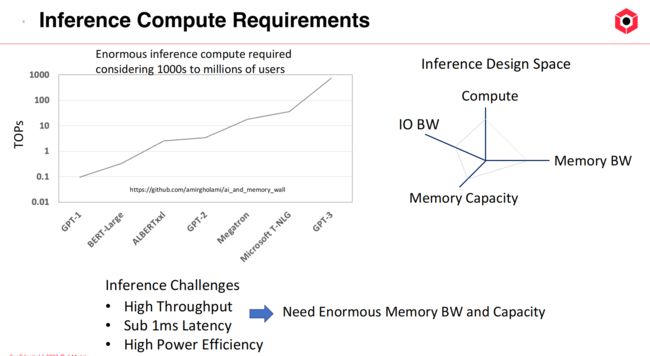

Large Scale Generative Inference Acceleration with Chiplets and In-Memory Compute

Speaker: J. Balachandran ( d-Matrix )

AI推理对计算系统的需求

针对AI推理设计的基于BoW互联的Chiplet架构模块图

通过BoW技术,该芯片实现了较好的可测性、较高质量的眼图。

,并展示了该芯片流片后的性能。

CXL-enabled systems start their roots on a die

Speaker: Siamak Tavallaei, CXL Advisor to the Board of Directors, CXL™ Consortium

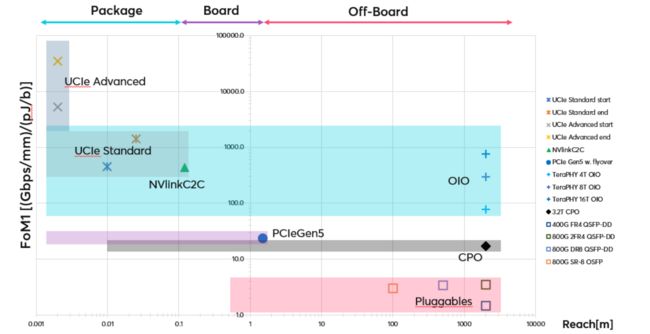

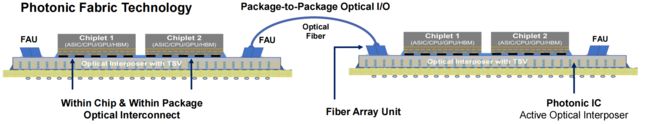

统一on-package和off-package的硅光互联技术:Optical IO

通过光介质层(Optical Interposer),使用光信号取代铜线实现chiplet间的信号互联,支持CXL、PCIe、UCIe、JEDEC(HBM)等工业界标准

OIO技术的带宽密度优势

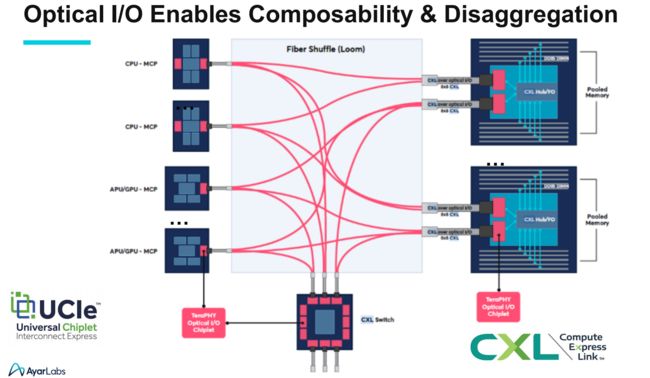

通过OIO接口将加速器、池化内存、CXL Switch建立互联

如下图所示,是一个基于CXL协议的互联网络。chip间互联的物理层使用PCIe协议;die间互联则使用UCIe协议,封装时同样采用OIO技术;CXL设备互联构成Photonics架构,之间长距离传输通过cable进行。

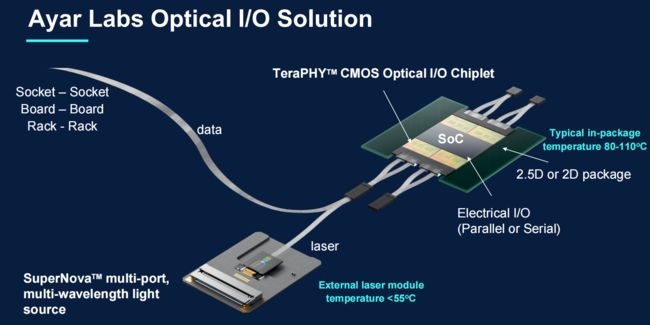

SuperNova为光源模块,用于信号传输,和设备的芯片接口和switch相连。

相关研究

K. Hosseini, et.al., “8 Tbps Co-Packaged FPGA and Silicon Photonics Optical IO”, OFC 2021

- 评

基于die技术生根发芽的搭载CXL的系统。先描述了CXL的应用场景、功能、技术架构、生态,再说明了chiplet技术进行各类硅组件互联的合理性,并提出了使用chiple设计时需关注的问题,并提出了统一on-package和off-package互联的解决方案Optical IO。即在on-package层,通过光介质层(Optical Interposer),使用光信号取代铜线实现chiplet间的信号传输,在off-package,使用光模块、cable等进行。

Chiplet-package Co-design CAD tools for Hetrogenerous-System-in-Package (HeSiP)

Speaker: Yarui Peng, Assistant Professor, Computer Science and Computer Engineering, University of Arkansas

对比传统和目标的chiplet芯片设计流程

新的chiplet设计流程增加对了chiplet划分、设计封装阶段的优化和分析等。

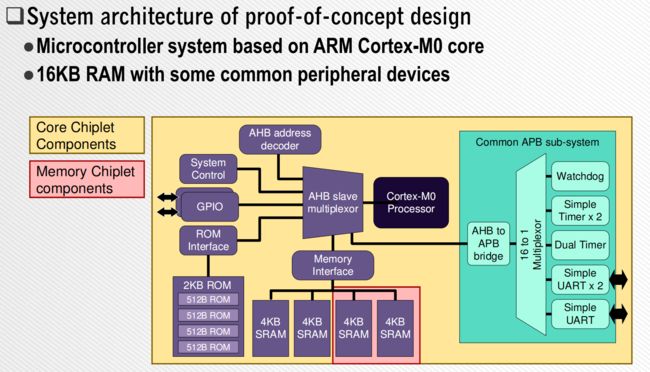

芯片系统架构和划分

设计团队将该MCU划分成core chiplet和8KB的memory chiplet。

相关研究

Md. Arafat Kabir, Yarui Peng, “Chiplet-Package Co-Design For 2.5D Systems Using Standard ASIC CAD Tools”, in Proc. Asia and South Pacific Design Automation Conference, pp. 351-356, Jan 2020.

- 评

用于异构封装系统的chiplet封装设计联合的CAD工具

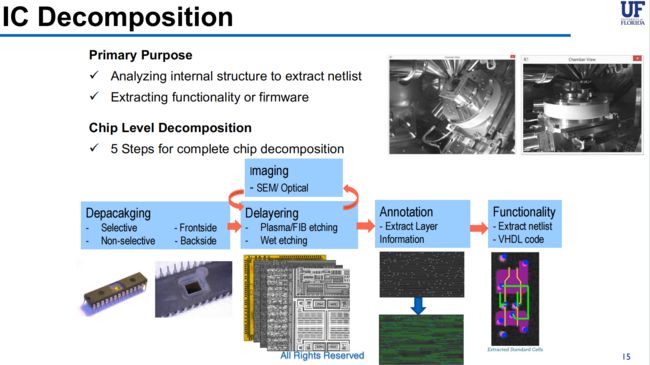

Physical Assurance of Microelectronics From Chiplets to Systems

Speaker: Navid Asadi (Assistant Professor, Director, Security and Assurance lab)

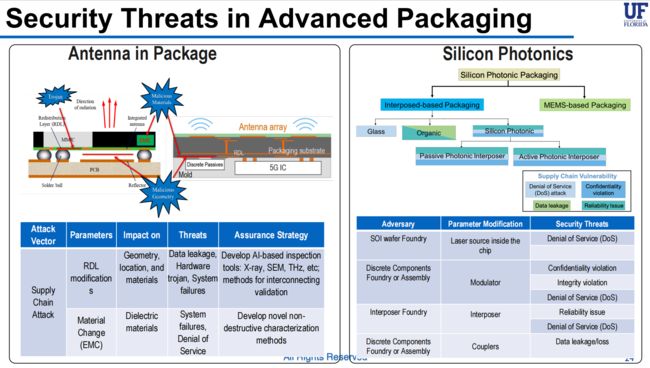

芯片多样的检测方法成为芯片攻击的重要手段

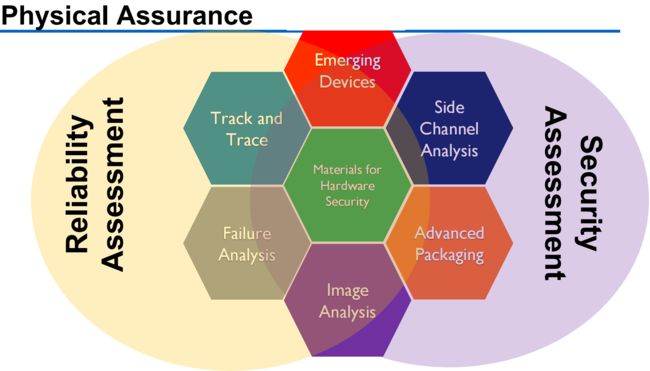

芯片物理保护的角度和手段

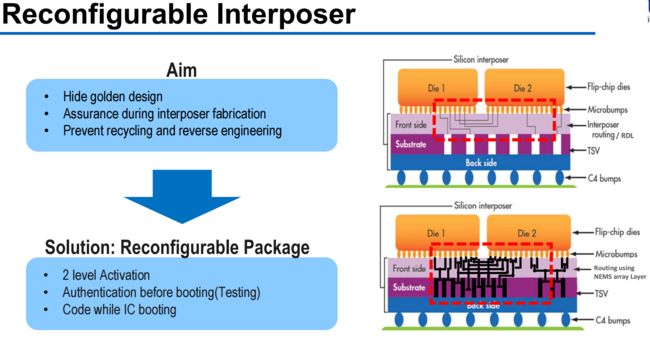

chiplet 可重配置的interposer实现芯片保护

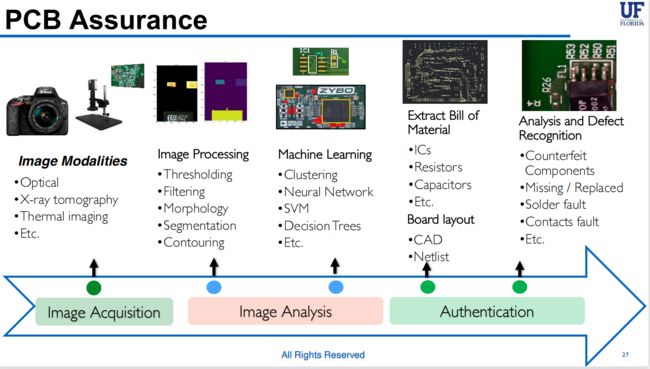

从板级系统角度确保物理安全

- 评

从Chiplet层级到系统层的微电子物理安全保护问题。本文探讨了芯片的物理安全保护问题,现代芯片面临这间谍破解、电磁破环等安全问题,该报告就chiplet架构芯片的interposer层、先进分装角度提出了几种防破解的方案,同时在PCB层级的系统层也提出了几种方案。

其他参考

(共封装光学CPO目前发展怎样?)[https://www.ednchina.com/technews/12276.html]

(OFC 2021: Ayar Labs实现1Tbps无差错的光芯片间信号互联)[https://cloud.tencent.com/developer/article/1844948]