timequest静态时序分析学习笔记——工具使用

这里我通过几条约束命令来讲解timequest工具的简单使用。

3.1 creat_clock约束命令

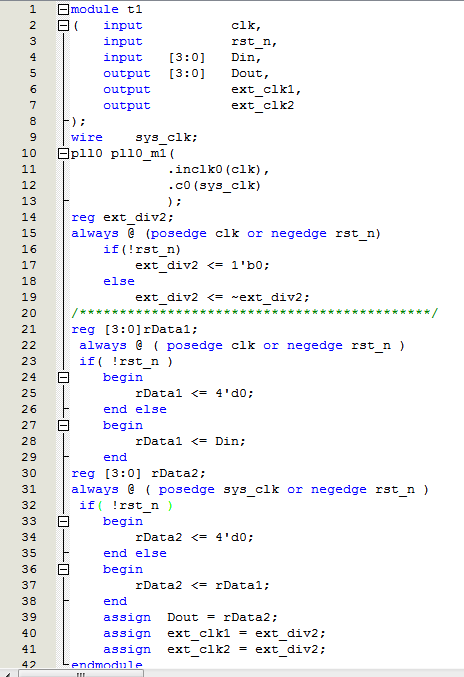

相关代码:

图27

第一步,在quartus ii软件tools下来菜单中找到timequest timing analyze选项并打开,出现如图27的会话框:

图 28

报告窗口:通过这个窗口,我们可以知道timequest都执行了哪些任务。

任务窗口:通过这个窗口,让timequest执行你要求的任务,比如点击report clocks,timequest就会在信息显示窗口你都约束了哪些时钟。

控制台:可以输入tcl命令让timequest执行相应任务。

信息显示窗口:timequest把当前任务的结果信息显示在该窗口。

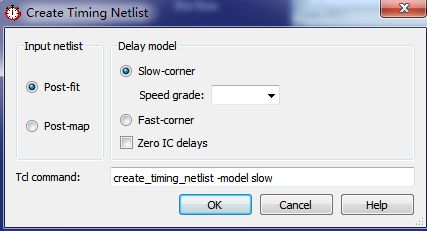

第二步,点击任务栏中的create_timing_netlist 或者在点击主菜单的netlist下拉菜单的create_timing_netlist选项,选择后面这种方式会出现如图28的会话框:

图29

首先看最左边的input netlist有post-fit和post-map之分,post-fit更接近物理结果(有优化),post-map更接近原型(没有优化)。右边的delay model有slow-corner和fast-corner之分,slow指timequest分析很糟糕的情况,比如FPGA工作在环境很差的情况下的模型,fast指timequest分析FPGA工作在正常的环境下,更接近实际的一种情况。Zero IC delays会无视一些网标基本单位的延迟。

通常情况下,我们会选择post-fit和slow-corner组合,如果在这样的情况下,设计都满足时序要求,那么我们的设计会更可靠。其实任务窗口中的create_timing_netlist默认就是这种组合,所以我们点击这个选项就可以了。

第三步,建立好网表以后,我们来创建第一条约束命令。

图30

这里对输入时钟clk进行了约束,时钟周期40ns,时钟名clk,点击run后,我们找到主菜单的constrants下拉菜单的 write SDC file选项并点击生成名为t1.out.sdc的SDC文件。

第四步,添加SDC文件,点击quartus ii里面主菜单assignments下拉菜单的setting选项弹出如图29的会话框,在会话框里找到timequest timing analyze选项,把SDC文件添加进来。

图31

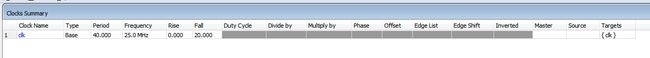

第五步,双击timequest timing analyzer任务窗口中的report clocks,然后在信息显示框里面可以看到我们刚刚约束的时钟,如图31:

图32

生成SDC文件的方式有几种,我用的是自己比较喜欢的一种方式。

在第二章说过 creat_clock还可以约束虚拟时钟,这种时钟不是FPGA内部使用的,它们是外部IC的时钟,在对I/O约束时要用到这样的时钟。由于之前已经生成了SDC文件,后面在添加约束命令的时候通过quartus ii软件主菜单edit选项下拉菜单的insert cronstrain选项中添加,这样添加的话命令就会直接添加进SDC文件里面,每次添加命令后,如果想要在timequest timing analyzer进行分析的话,必须从新加载SDC文件才行。如图33所示,依次双击Reset Design、Read SDC File、Update Timing Netlist即可。

图33

通过creat_clock创建虚拟时钟,我这里创建了两个虚拟时序:ext1_clk和ext2_clk。看SDC文件和timequest timing analyzer信息显示框有什么变化,如图34:

图34

看type那列,ext1_clk和ext2_clk的类型是virtual。

3.2 creat_generated_clock

通过代码可以知道,这里的时钟有第二章讲creat_generated_clock约束命令作用时的1,2,4条,sys_clk对应第1条作用,ext_div2对应第4条作用,ext_clk1和ext_clk2对应第2条作用。然后我们通过creat_generated_clock会话框对这3种进行约束,如图35:

SDC文件相应的约束命令

图35

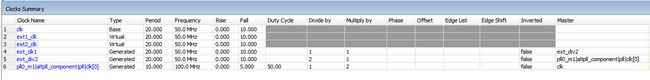

如图36,在任务窗口双击report clocks后观察信息显示窗口的时钟情况,这里能看到每一个被约束的时钟,它们各自的周期、频率、类型,源时钟等。

图36

如图37,在任务窗口双击report timing后观察信息显示窗口的时钟情况,这里可以看到timequest都分析了哪些路径,可以发现,输入Din到rData1和rData2到输出Dout之间的路径没有分析,那是因为timequest在分析的时候都是分析两个寄存器间的路径,而不是分析寄存器到管脚的路径,FPGA管脚都是与外部IC打交道,所以这里需要添加set input delay和set output delay约束,timequest才能分析这些路径。

图37

现在来看看这几条命令都分别约束的哪几个时钟:

约束pll,对应sys_clk: derive_pll_clocks

约束ext_div2 : create_generated_clock -name ext_div2 -source [get_pins {pll0_m1|altpll_component|pll|clk[0]}] -divide_by 2 [get_keepers {ext_div2}]

约束ext_clk1和ext_clk2: create_generated_clock -name ext_clk1 -source [get_keepers {ext_div2}] [get_ports {ext_clk1}]

create_generated_clock -name ext_clk2 -source [get_keepers {ext_div2}] [get_keepers {ext_div2}]

3.3小结

这章通过两个约束命令讲了如何使用timequest分析工具,由于在第二章里面对每条约束命令的含义都讲过了,我想通过对这两个约束命令的学习,也能添加其它约束命令和分析了,想要对工具有更多的了解,建议阅读TimeQuest_User_Guide.pdf,这上面讲得很清楚。