(一)ZYNQ + VIVADO 笔记:Hello World

第一部分 前言

今天开始米联课系列教程的学习,不知道为什么他们自己的官网(http://www.osrc.cn/forum.php?mod=viewthread&tid=1239&extra=page%3D1)上的视频播放不出来,但是程序包是有的,所以我是在腾讯视频和优酷视频上看的教程,这是链接http://v.qq.com/vplus/ba9331b3ac429787def1e7c7ee68744c。然后米联客这个团队出了一本书,我先自己看一下,如果好用的话再分享给大家。这个系列博客之后只做笔记使用,所以不会特别详细的介绍具体的步骤(想详细的看步骤请看相应的视频),只给出一些关键的、值得做笔记理解总结的部分。

还有一点与这个视频不同之处在于,我使用的是ZedBoard Zynq Evaluation and Development Kit这套开发套件,而视频中使用的是Miz702这块板子,所以会对照给出相应的一些东西

第二部分 笔记

2.1 在进行板上已有资源的使用时,要学会查看原理图进行对比,这是zedboard的原理图文件http://www.zedboard.org/sites/default/files/documentations/ZedBoard_RevD.2_Schematic_130516.pdf。

如上图所示,IO的使用上是对应的。

2.2 Zynq7的系统公共资源及特性

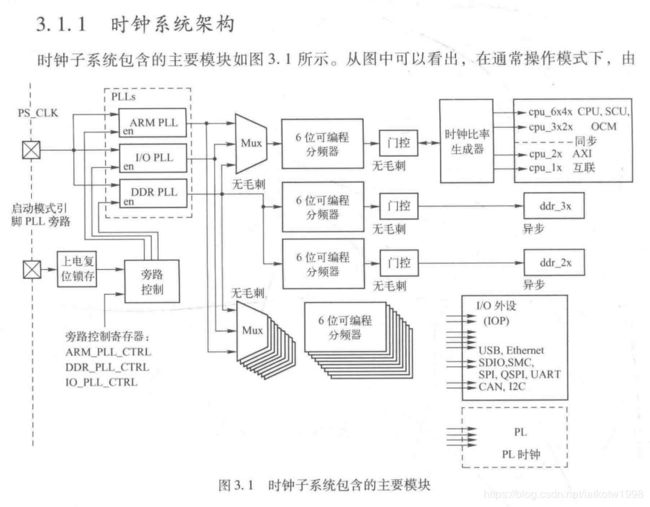

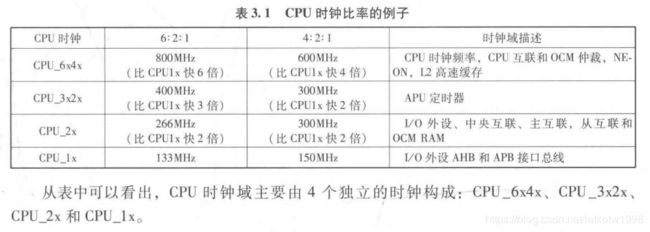

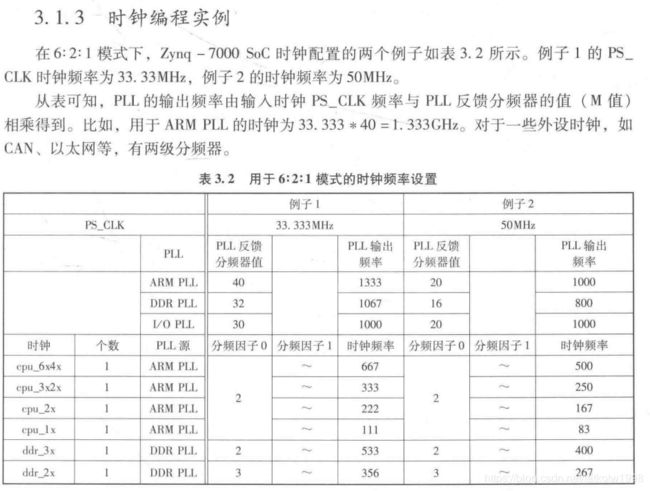

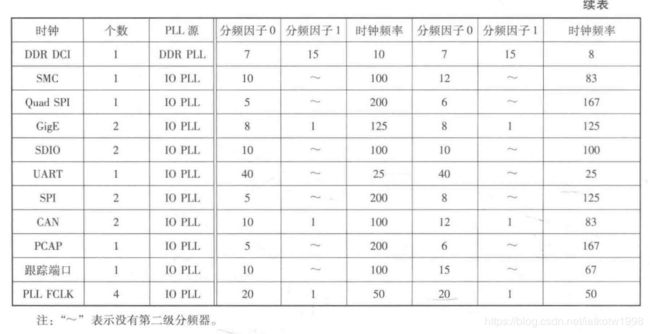

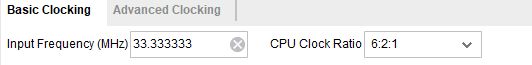

(这部分内容的详细介绍在https://download.csdn.net/download/iatkotw1998/10840227第二本书的第三章有非常详细的介绍)这里截取一部分可以帮助理解VIVADO对应的时钟部分的设置。

随后还介绍了所有部件包括基本时钟、DDR、I/O外设时钟、GPIO、PL在内的时钟生成方式以及复位系统的层次,详细了解请自行查阅。

上述很多的内容其实是可以对应上vivado界面的选择内容的,如Ratio比例等等

2.3 工程示例步骤,在教程中,作者分别示例了Hello World、DDR、LWIP网络通信的例程。但就本篇笔记而言,只给出步骤分析即可了。其实在上一篇博客,流水灯的分析中,有很多步骤已经说明的很详细了,但是有些步骤却是之前没有补充的,这里加以说明。

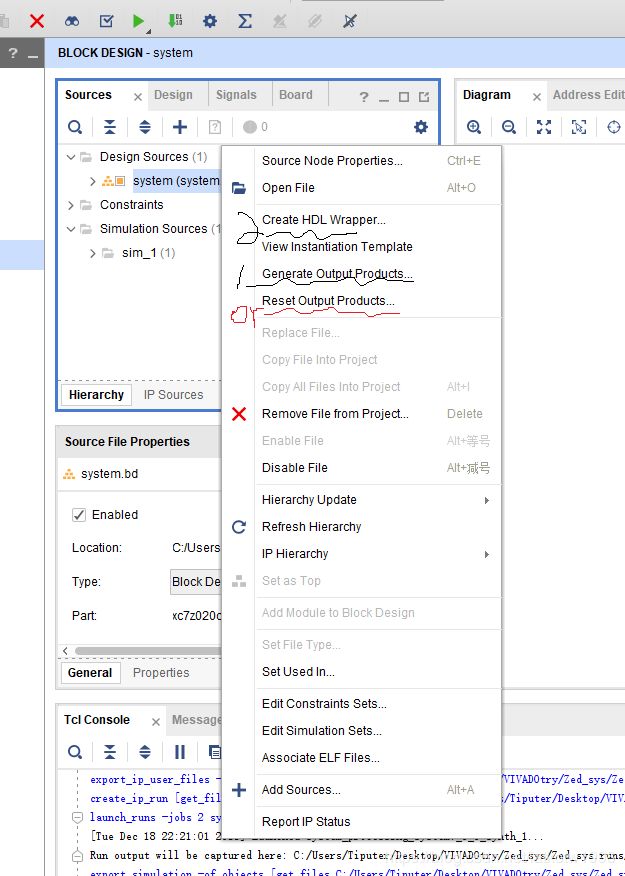

2.3.1 在核对时钟后,要继续核对DDR的Memory Part,查阅原理图即可知,如下图

型号125后默认即是K

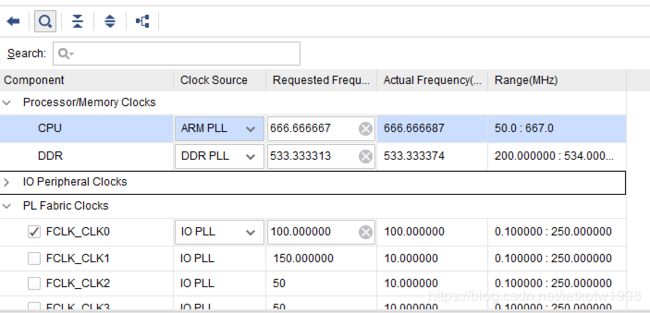

2.3.2 bank电平,然后捎带介绍一下,把两个时钟接口连起来的目的是把PS的时钟接入PL部分,当然这里我们暂时用不到PL部分的资源。

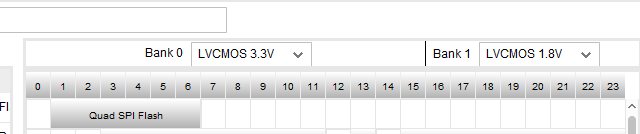

2.3.3 随后按顺序选择Generate生成相关文件,随后再产生HDL Wrapper。如果产生报错的话可以选择reset将原有文件清楚后再生成一遍。

2.3.4 再生成相应的bitstream,会耗费一点时间。

2.3.5 再 export hardware(记得include bitstream)和 lauch sdk

2.4 SDK 部分

2.4.1 打开SDK后最先会有一个基础的文件,提供相关的配置,以及下图地址的映射都有详细的给出

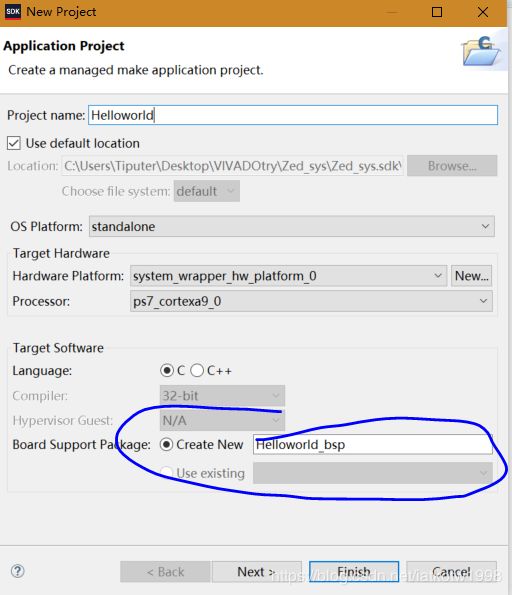

2.4.2 对于多个工程可以共用一个DSP包,如下图画线部分其实只需要新建一次就行,像之后的DDR等可以直接用已存在的就行。

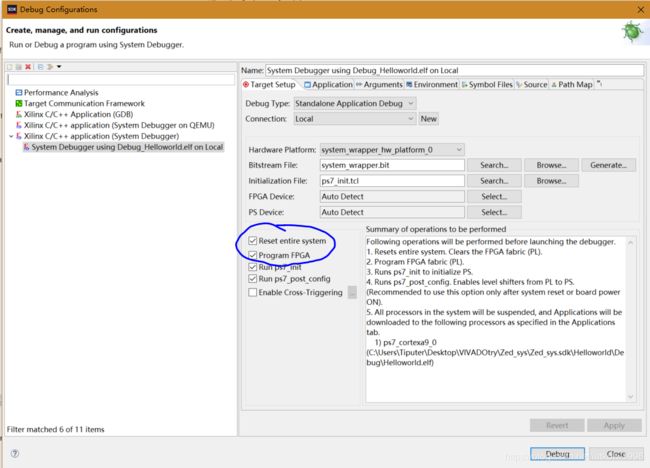

2.4.3 然后就是要注意这个debug configuration,因为之前也看过其他的教程,是另外一种专门设置串口的界面,估计是老版本的vivado了,新版本直接设置vivado setup就好。另外要记得勾选上下图的两项

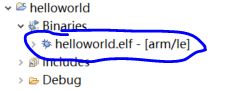

否则会需要另外选择program fpga。同时如果不reset的话,另作更改后的程序又得重新手动reset一遍较为麻烦,所以最好勾选上。还有就是前面双击产生的一定得是 using Debug_Helloworld.elf on local 而不能直接是 on local,否则会跑不出来,进行zedboard重启再新建,注意下图的文件有没有生成,因为最终要下载的就是这个文件。

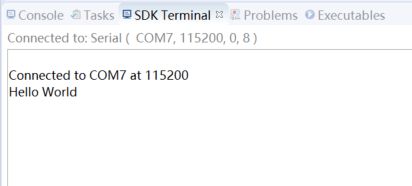

最后显示Hello World如图

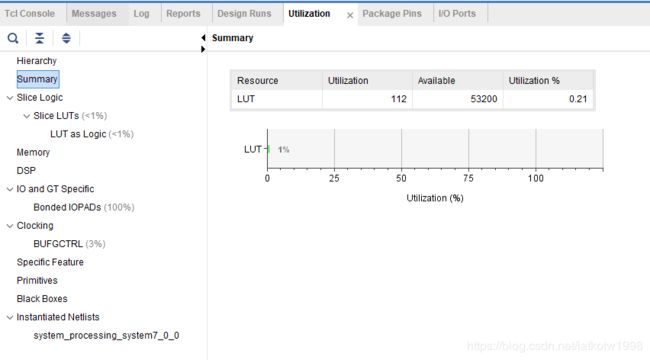

2.4.4 对helloworld这一单项做一个小总结,虽然在我们看来的确是只用到了PS模块,但是在Utilization Summary中仍然显示占用了LUT资源

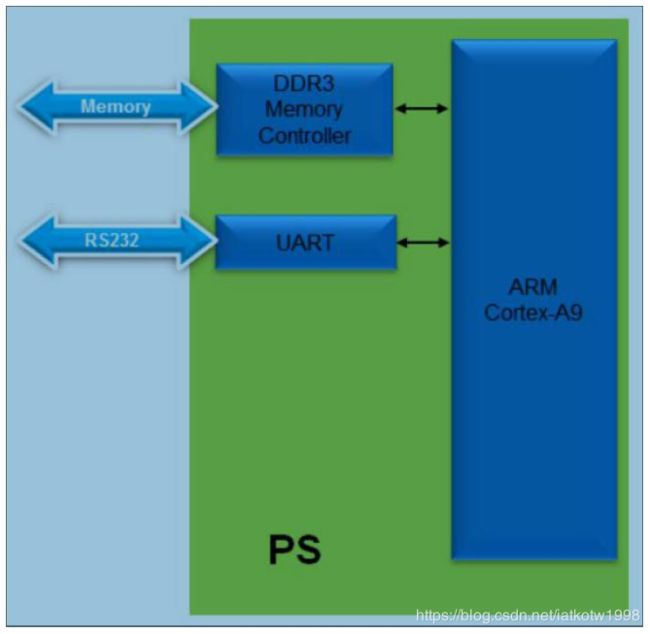

可见,在 export hardware 时,必须 include bitstream,因为bitstream中包含了对zynq器件中布局和布线的描述。而 helloworld 工程的架构图如下

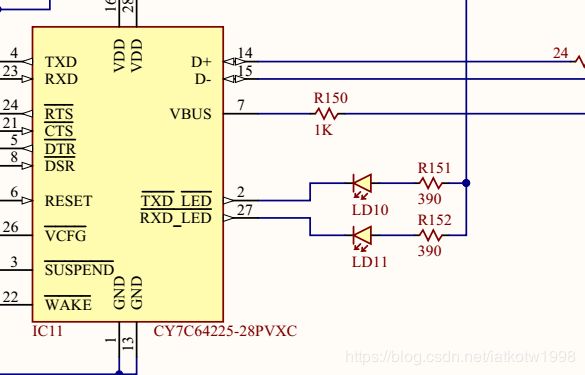

2.5 之后的 memory 和 ddr 例程也都尝试了正常,但是出现过板子上的串口接口黄灯亮,并且电脑上的端口没有任何反应的情况,可以查看电路图

如图所示,理应是被强行拉低提示通信出现错误,如果是LD11亮,说明电脑发端出现错误,可以尝试重新连接或者重启SDK。

然后提醒一下,这一视频中测试的内存是片上内存,测试的DDR是外设DDR,所以如果DDR能够成功说明前面更改的 DDR Part 设置是正确的。

-----------------------------------------------------完,欢迎指正,互相学习------------------------------------------------------------