Ni Multisim中规模集成电路设计

中规模集成电路设计

日期:2018.12.22 指导老师: 年级班级:

学生信息 院系:

实验要求

1、熟悉典型芯片的功能,灵活使用各类芯片如四位二进制加法器、编码器译码器、多路选择器和分配器;同步或异步可逆计数器、寄存器。

2、采用典型芯片设计例题或习题,并通过软件仿真实现其功能。

实验说明

为了帮助大家更好的理解中规模集成电路设计,本实验实现了几个比较典型的电路设计,

分别是,四位二进制全加全减器,译码器,多路选择器,同步可逆计数器,以及寄存器。

实验步骤

实验一:四位二进制全加全减器

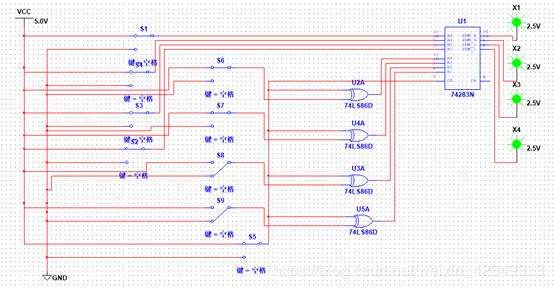

实验主要器材:

4位并行加法器(74283N),异或门(74LS86N),灯泡(probe)

实验思路:

A,B,分别为两个4位二进制数,在C0端口接入一个M(功能选择变量),M=0时,实现全加器A+B,M=1时,实现全减器A-B,运算结果在F端口输出,输出的结果通过灯泡来体现。减法采用补码运算。

逻辑电路图:

实验现象:

当A,B的多组代值测试,发现与计算结果始终一致,实验成功。

实验二:译码器

实验目的:

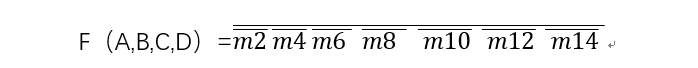

用与非门和译码器实现逻辑函数:

F(A,B,C,D)=Σm(2,4,6,8,10,12,14)

实验器材:

3-8线译码器(74LS138D),8输入与非门(7430N),灯泡(probe)

实现思路:

显然用一个3-8线译码器是实现不了的,所以这里用了两个,首先将函数化简为

将逻辑变量B,C,D分别接到片1和片2的输入端C,B,A(对应的A2,A1,A0),逻辑变量A接至片1的使能端`S2,和片2的使能端S1。这样A=0,时,片1工作,片2就禁止,由片1来产生`m0~`m7;A=1时,片2工作,片1禁止,由片2来产生`m8~`m15。

逻辑电路图:

实验现象:

测试多组数据发现与函数功能一致,实验成功。

实验三:多路选择器

实验目的:

用4路MUX实现4变量逻辑函数的功能

F(A,B,C,D)=Σm(0,2,3,7,8,9,10,13)

实验器材:

4路MUX(MUX_4TO1),与门(7408N),非门(7404N),或门(7432N)

实验思路:

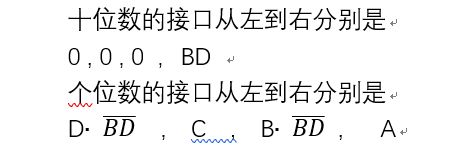

选A,B为选择控制变量,与A1,A0端口连接(这里是B,A),然后将函数进行变化

逻辑电路图:

实验现象:

测试多组数据发现与函数功能一致,实验成功。

实验四:同步可逆计数器(模12)

实验器材:

4位 二进制同步可逆计数器(74193N),与非门(7400N),与门(7408N),非门(7404N),数码管(DCD——HEX——BLUE),时钟脉冲

实验思路:

预置口接的是借位的输出口,所以有借位的时候就会重置,这样方便了很多,这里用了两个数码管来实现输出的结果,一个是十位数,一个是个位数,在模12的计数器里面只有1011,1010,大于10,所以当A3,A1同时为零时十位为1,其他都是0,个位数也是只有他们同时为1的时候才会有变化,当他们同时为1的时候我们只需将A3,A1都为0,个位结果不变。这里是用与非门,与门,非门来实现的。

逻辑电路图:

实验现象:

数码管的数字从11到0,实现了模12的计数器,实验成功。

实验五:寄存器

实验目的:

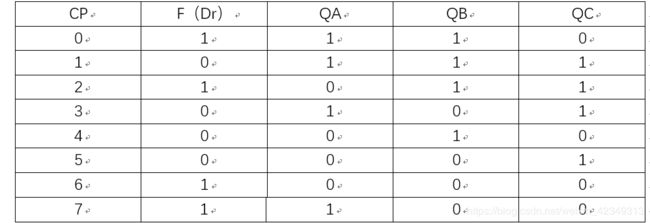

用74194和适当的逻辑门实现序列为01110100的序列发生器

实验器材:

寄存器(74194N),时钟脉冲,逻辑分析器,异或门(74136N),与门(7408N),非门(7404N),或门(7432N)

实验思路:

将序列110作为初始状态,电路在时钟的作用下,状态变化和右移输入值表如下:

由表可以得出函数F的表达式

逻辑电路图:

实验现象:

产生了01110100的序列,试验成功。

实验心得

- 就是仪器问题了,可能找不到,所以我把所有用到的仪器都列出来了。

- 实验2,3,4中软件中的接口与书上有点不一样,所以我就接错了,得不出正确的结果,在书上接口是A3,A2,A1,A0,但是一起中的是A,B,C,D但是D是高位,A是低位,所一定要仔细。

- 在实验4中,老师建议我们用4个二进制的数来实现输出,但是我们觉得用数码管更加美观,于是使用了数码管,但是数码管表示模12有点困难,讨论后还是得出了解决方案。

- 寄存器书上面实现的与要求的相反,我在这里实现的是正的序列(就把原来的序列反过来再按书上的方法实现)。