- FPGA 学习笔记:Vivado 2020.2 MicroBlaze MIG 测试 DDR3 篇二

zhangsz_sh

FPGA开发技术fpga开发学习

前言因为FPGADDR3测试的工程搭建步骤比较的多,所以分成几篇来写,这样利于把复杂的事情拆分,利于理解与实际的操作上一篇搭建了初步的HelloWorld工程,还没写什么代码或者改什么配置,所以FPGA开发,并不是上来就写VerilogHDL,而是要把更多的时间用在:目标是什么?DDR3测试,正常DDR3能否当RAM一样使用清楚要做什么,这里通过搭建嵌入式软核处理器的方式,快速验证实现与验证:搭建

- 基于 Verilog 的经典数字电路设计(1)加法器

新芯设计

1专栏革新中禁止订阅!!!FPGAVerilog加法器数字IC设计IC

基于Verilog的经典数字电路设计(1)加法器版权所有,新芯设计,转载文章,请注来源引言一、半加器的Verilog代码实现和RTL电路实现一、全加器的Verilog代码实现和RTL电路实现引言 加法器是非常重要的,它不仅是其它复杂算术运算的基础,也是CPU中ALU的核心部件(全加器)。两个二进制数之间的算术逻辑运算例如加减乘除,在数字计算机中都是化为若干步加法操作进行的,因此,学好数字电路,从

- FPGA学习——verilog捕捉信号上升沿下降沿

or_to

FPGAfpga开发学习

在FPGA使用中,常常需要进行信号的边沿检测,如在串口通信中,需要检测接收信号的下降沿来判断串口的的起始位。常用的方法就是:设计两个一位的寄存器,用来接收被检测的信号,系统时钟来一次记一次输入信号,如果用了两个寄存器直接异或就可以了;使用高频的时钟对信号进行采样,因此要实现上升沿检测,时钟频率至少要在信号最高频率的2倍以上,否则就可能出现漏检测。代码如下:moduleedge_detect(sys

- FPGA学习篇——Verilog学习4(常见语句)

ooo-p

Verilog学习fpga开发学习

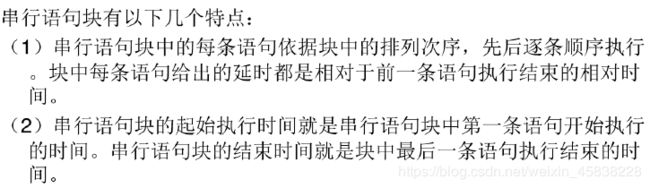

1.1结构语句结构语句主要是initial语句和always语句,initial语句它在模块中只执行一次,而always语句则不断重复执行,以下是一个比较好解释的图:(图片来源于知乎博主罗成,画的很好很直观!)1.1.1initial语句initial语句它在模块中只执行一次。它常用于测试文件的编写,用来产生仿真测试信号(激励信号),或者用于对存储器变量赋初值。语法格式:initialbegin.

- FPGA学习笔记(二)Verilog语法初步学习(语法篇1)

贾saisai

FPGA学习fpga开发学习1024程序员节

FPGA系列文章目录一、FPGA学习笔记(一)入门背景、软件及时钟约束二、FPGA学习笔记(二)Verilog语法初步学习(语法篇1)三、FPGA学习笔记(三)流水灯入门FPGA设计流程四、FPGA学习笔记(四)通过数码管学习顶层模块和例化的编写五、FPGA学习笔记(五)Testbench(测试平台)文件编写进行Modelsim仿真六、FPGA学习笔记(六)Modelsim单独仿真和Quartus

- Verilog学习方法—基础入门篇(一)

博览鸿蒙

FPGAfpga开发

前言:在FPGA开发中,VerilogHDL(硬件描述语言)是工程师必须掌握的一项基础技能。它不仅用于描述数字电路,还广泛应用于FPGA的逻辑设计与验证。对于初学者来说,掌握Verilog的核心概念和基本语法,是深入FPGA开发的第一步。本篇文章将从Verilog基础入门的角度,帮助你快速建立学习框架,逐步掌握Verilog的使用方法。1.了解Verilog的基本概念1.1什么是Verilog?V

- 【从零开始学习计算机科学】数字逻辑(五) Verilog HDL语言

贫苦游商

学习fpga开发数字逻辑verilogHDL硬件开发逻辑电路

【从零开始学习计算机科学】数字逻辑(五)VerilogHDL语言VerilogHDL语言8位全加器8位计数器2位比较器三态驱动器VerilogHDL模块的结构模块声明。端口定义。信号类型。功能描述verilog描述级别verilog关键字verilog标识符编写VerilogHDL源代码的标准数据类型常量变量nets型变量register型变量reg型变量运算符及表达式算术运算符逻辑运算符位运算符

- 基于FPGA的图像中值滤波Verilog实现及MATLAB辅助验证

CodeWG

fpga开发matlab开发语言

基于FPGA的图像中值滤波Verilog实现及MATLAB辅助验证图像处理是计算机视觉和图像识别领域的重要组成部分。其中,中值滤波是一种常用的图像去噪方法,广泛应用于图像增强、边缘检测和特征提取等任务中。本文将介绍基于FPGA的图像中值滤波Verilog实现,并通过MATLAB进行辅助验证。首先,我们需要了解什么是中值滤波。中值滤波是一种非线性滤波器,它的原理是将图像中每个像素的灰度值替换为该像素

- verilog练习:HRPWM 模块设计

啄缘之间

Verilog项目练习学习资料总结fpga开发学习svuvmverilog测试用例

文章目录前言1.HRPWM代码示例:1.1关键设计说明:2.HRPWM温度补偿和动态校准2.1关键增强功能说明:2.2校准流程验证方法:2.3性能优化建议:前言需要考虑如何用SystemVerilog实现这些功能。首先,模块的输入输出端口应包括时钟、复位、占空比设置、使能信号,以及PWM输出。内部可能需要计数器、比较寄存器、MEP控制逻辑。MEP的实现可能需要一个微边沿计数器,在每个主时钟周期内生

- 用verilog实现3-8译码器和全加器

珠泪美人鱼

fpga开发

提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档文章目录前言一、pandas是什么?二、使用步骤1.引入库2.读入数据总结提示:以下是本篇文章正文内容,下面案例可供参考一、用verilog实现3-8译码器首先在一个磁盘上创建一个文档。如下图:在文档中在创建两个文档来储存项目和代码。如图:之后在quartus上建好项目后,填写代码。代码如图:

- 【HDLbits--FSM状态机】

中古传奇

HDLHDL

HDLbits--FSM状态机1.6FSM介绍1.6FSM示例1单输入单输出FSM2双输入单输出FSM3真指标状态4MooreFSMdemo5时序图和状态图写状态机【博客首发于微信公众号《漫谈芯片与编程》,欢迎大家关注,多谢大家】1.6FSM介绍在Verilog中,有限状态机(FiniteStateMachine,FSM)是一种用于描述系统行为的模型,通常用于控制逻辑的设计。FSM由一组状态、状态

- 验证环境中为什么要用virtual interface

m0_71354184

systemverilog

在UVM(UniversalVerificationMethodology)中使用virtualinterface的主要目的是解决SystemVerilog接口(interface)的静态特性与UVM验证环境的动态特性之间的不匹配问题。1.解决静态与动态的绑定问题SystemVerilog接口(interface)是静态的:在编译时确定,无法直接用于动态创建的UVM对象(如driver、monit

- 6. 示例:用mailbox实现生产者-消费者模型

啄缘之间

UVM学习计划表学习verilog测试用例svuvm

文章目录前言示例一:生产者-消费者模型1示例二:生产者-消费者模型2示例三:生产者-消费者模型3示例四:生产者-消费者模型41.完整代码示例2.仿真步骤3.关键代码解析4.波形与日志分析5.常见问题与解决6.扩展练习前言以下是一个完整的SystemVerilog示例,使用mailbox实现生产者-消费者模型,包含详细注释、仿真步骤及预期结果。代码兼容主流仿真工具(如CadenceXcelium的x

- 【Verilog--Procedures】

中古传奇

HDLHDL

Verilog--Procedures1.4Procedures1.4.0CombVSClocked1.4.1always-if1.4.1.1Avoidlatches1.4.2case【博客首发于微信公众号《漫谈芯片与编程》,欢迎大家关注,多谢大家】电路模块是由通过导线连接的逻辑门组成,任何电路都可以表示为模块和赋值语句的某种组合。但有时候这不是描述电路的方便方法。过程(其中always是一个例子

- Linux下VCS与Verdi联合仿真(Verilog与VHDL混仿)

超能力MAX

fpga开发

1.介绍本篇简单介绍一下如何通过VCS与Verdi实现混合仿真,在学习过程中也遇到了很多头疼的问题,因此通过一些例子简要总结一下,当然,也希望对各位小伙伴有所帮助。很多公司ASIC设计所使用的还是更加专业的EDA软件,即Synopsys下的VCS、Verdi这种(Vivado大多针对于自家FPGA),VCS编译速度极快,仿真效率高,Verdi支持信号追溯、无缝增加信号波形等功能。2.使用环境:Li

- FPGA基础知识----第三章 第2节 综合和仿真

原来如此呀

FPGA学习之旅fpgaverilog

第2节综合和仿真2.1综合Verilog是硬件描述语言,顾名思义,就是用代码的形式描述硬件的功能,最终在硬件电路上实现该功能。在Verilog描述出硬件功能后需要使用综合器对Verilog代码进行解释并将代码转化成实际的电路来表示,最终产生实际的电路,也被称为网表。这种**将Verilog代码转成网表的工具就是综合器**。上图左上角是一段Verilog代码,该代码实现了一个加法器的功能。在经过综合

- (14)FPGA与GPU区别

宁静致远dream

FPGA入门与提升(培训课程)fpga开发

(14)FPGA与GPU区别1文章目录1)文章目录2)FPGA入门与提升课程介绍3)FPGA简介4)FPGA与GPU区别5)技术交流6)参考资料2FPGA入门与提升课程介绍1)FPGA入门与提升文章目的是为了让想学FPGA的小伙伴快速入门以及能力提升;2)FPGA基础知识;3)VerilogHDL基本语法;4)FPGA入门实例;5)FPGA设计输入,包括代码输入、原语输入;6)FPGA设计技巧;7

- lattice hdl实现spi接口

寒听雪落

FPGA专栏_verilogfpga开发

在lattice工具链中实现SPI接口通常涉及以下步骤:定义硬件SPI接口的管脚。配置SPI时钟和模式。编写SPI主机或从机的控制逻辑。展示了如何在Lattice工具链中使用HDL语言(例如Verilog)来配置SPI接口:lattice工程顶层:spi_slave_top.v`timescale1ns/1psmodulespi_slave_top(inputwireCLK,//Systemclo

- verilog基础知识

寒听雪落

FPGA专栏_verilogfpga开发

一,Verilog和VHDL区别全世界高层次数字系统设计领域中,应用Verilog和VHDL的比率是80%和20%;这两种语言都是用于数字电路系统设计的硬件描述语言,而且都已经是IEEE的标准。VHDL是美国军方组织开发的,VHDL1987年成为标准;Verilog是由一个公司的私有财产转化而来,Verilog是1995年成为标准。Verilog有更强的生命力,后来Verilog成为IEEE标准这

- 大学实验课设无忧 ------ 基于FPGA动态数码管数字时钟

FPGA猫

大学实验课设无忧fpga开发

一、前言动态数码管显示是FPGA开发中常见的应用场景之一,尤其在数字时钟、计数器等设计中广泛应用。本文将介绍如何使用FPGA实现一个基于动态数码管的数字时钟,能够显示时、分、秒。该设计基于XilinxFPGA开发板,使用VerilogHDL编写代码,适合初学者学习和参考。二、设计思路本设计分为以下主要模块:时钟分频模块:将系统时钟分频为1Hz信号,用于计时或符合设计需求的频率。动态扫描模块:控制数

- FPGA设计怎么学?薪资前景好吗?

博览鸿蒙

FPGAfpga开发

FPGA前端设计和各岗位之间有着很多联系,是一个薪资待遇高,前景发展好的岗位。但这个岗位的门槛也比较高,很多人不知道怎么学习,下面就和宸极教育一起来了解一下吧。数字前端设计必备技能1、熟悉数字电路设计2、熟悉Verilog或VHDL3、熟悉异步电路设计4、熟悉FIFO的设计5、熟悉UNIX系统及其工具的使用6、熟悉脚本语言Perl、Shell、Tcl等7、熟悉C/C++语言、SystemVeril

- [Verilog]带使能端的级联BCD码计数器 - 以时钟计数器为例

Jason_Tye

fpga开发

问题描述//模块声明moduletop_module(inputclk,inputreset,inputena,outputpm,output[7:0]hh,output[7:0]mm,output[7:0]ss);前置知识:BCD码:将十进制数的每一位(0~9)按序,用4位2进制数表示Decimal=[3:0]Binary(78)10=(0111,1000)BCDDecimal=[3:0]\Bi

- [Verilog]模块实例化驱动的理解

Jason_Tye

fpga开发

笔者在复习刷题HDLBits时,对模块实例化时,接口的驱动有了更深理解.问题描述实现100位的带涟漪进位(ripple-carry)的全加器处理过程这是一个纯组合逻辑电路,除了可能在CombinationalBlocksalways@(*)中进行的赋值外,无需reg,所以默认的wire类型不予显式.首先实现单位全加器full_addermodulefadd(inputa;inputb;inputc

- - `always @(posedge opt_txclk)` 触发后,调用内部有 `@(posedge opt_txclk)`的task

零度随想

fpga开发

问题背景always@(posedgeopt_txclk)触发后,调用task。task内部还有@(posedgeopt_txclk),但在下一个时钟沿到来之前,always块会不会重新触发,从而导致错误。Verilog的事件调度机制always@(posedgeopt_txclk)每当opt_txclk出现上升沿时,always块会被触发,进入执行状态。任务中的@(posedgeopt_txcl

- 均薪23W还缺人,FPGA工程师到底有多重要?

博览鸿蒙

FPGAfpga开发

近两年,随着FPGA行业的快速发展,FPGA工程师的需求量持续增长。FPGA技术在通信、人工智能、自动驾驶、数据中心等领域的广泛应用,使得这一岗位变得尤为重要。尤其是在高性能计算、边缘计算等场景下,FPGA凭借其高并行计算能力和灵活性,成为不可或缺的技术方案。FPGA工程师的核心职责FPGA工程师主要负责FPGA的开发、调试和优化,具体包括:逻辑设计与实现:使用Verilog/VHDL等硬件描述语

- Verilog 实现 FPGA 复杂算法的案例

百态老人

fpga开发

在数字电路设计领域,FPGA(现场可编程门阵列)因其灵活性和高性能而备受青睐。有许多利用Verilog实现FPGA复杂算法的案例。例如,有一个项目是在FPGA中用Verilog实现开方运算。该项目充分利用Verilog的强大功能,通过深入理解FPGA的内部结构优化代码资源利用率,采用经典数学算法确保计算结果的准确性和高效性。具有高效性、可移植性和易用性等优势,适用于对实时性要求较高的应用场景,为开

- XY2-100协议解析

李逍遥lzx

fpga开发

前言XY2-100及XY2-100-E协议被广泛地应用于激光振镜的控制中,本文将从激光振镜控制原理,接口引脚定义,协议时序,以及verilog代码实现实现这几个角度展开本文。本文参考RAYLASE的官方文档一、激光振镜的工作原理激光振镜所使用的电机为检流式电机,检流式电机工作原理类似于电流计,电机的旋转角度会随着输入电压变化.当转动的电磁力矩与回复力矩平衡时,电机偏转到位,此时的偏转角与输入电压成

- XY2-100的Verilog实现

csdn_gddf102384398

fpga开发

xy2_100.vmodulexy2_100(inputclk,inputtx_init,//当产生上升沿时,开始发数据inputwire[15:0]x_pos,inputwire[15:0]y_pos,inputwire[15:0]z_pos,outputclk_2MHz_o,//输出2MHz时钟outputsync_o,outputx_ch_o,outputy_ch_o,outputz_ch_

- 【了不起的芯片底层】-verilog设计实例

huxixi_2

数字ICfpga开发

序列检测器作用:从一串码流中检测出指定序列10010,监测到一个序列后就输出一个高电平。设计状态转换机制:初始是IDLE态,然后输入1后进入A状态,输出0;输入0依然保持IDLE,输出0;在A状态,输入0进入B状态,输出0;输入1进入F中间态,输出0;在B状态,输入0进入C状态,输出0;输入1进入G中间态,输出0;.....以此类推所有状态。一共8个状态,需要3位记录状态的寄存器,实现代码如下:/

- Verilog 语法篇 硬件描述语言

7yewh

【FPGA知识点笔记汇总】fpga开发硬件工程驱动开发arm开发物联网iot

Verilog是一种硬件描述语言,用于设计、模拟和综合数字电路和系统。它主要用于描述ASIC(专用集成电路)或FPGA(现场可编程门阵列)等硬件设备的结构和行为。定义与用途:Verilog是一种硬件描述语言(HDL),主要用于数字电路的建模、仿真、综合与验证。设计人员利用它来描述电路的结构、行为以及时序关系,从而生成实际的硬件电路(如FPGA或ASIC)。发展背景:1984年,PhilMoorby

- jQuery 键盘事件keydown ,keypress ,keyup介绍

107x

jsjquerykeydownkeypresskeyup

本文章总结了下些关于jQuery 键盘事件keydown ,keypress ,keyup介绍,有需要了解的朋友可参考。

一、首先需要知道的是: 1、keydown() keydown事件会在键盘按下时触发. 2、keyup() 代码如下 复制代码

$('input').keyup(funciton(){

- AngularJS中的Promise

bijian1013

JavaScriptAngularJSPromise

一.Promise

Promise是一个接口,它用来处理的对象具有这样的特点:在未来某一时刻(主要是异步调用)会从服务端返回或者被填充属性。其核心是,promise是一个带有then()函数的对象。

为了展示它的优点,下面来看一个例子,其中需要获取用户当前的配置文件:

var cu

- c++ 用数组实现栈类

CrazyMizzz

数据结构C++

#include<iostream>

#include<cassert>

using namespace std;

template<class T, int SIZE = 50>

class Stack{

private:

T list[SIZE];//数组存放栈的元素

int top;//栈顶位置

public:

Stack(

- java和c语言的雷同

麦田的设计者

java递归scaner

软件启动时的初始化代码,加载用户信息2015年5月27号

从头学java二

1、语言的三种基本结构:顺序、选择、循环。废话不多说,需要指出一下几点:

a、return语句的功能除了作为函数返回值以外,还起到结束本函数的功能,return后的语句

不会再继续执行。

b、for循环相比于whi

- LINUX环境并发服务器的三种实现模型

被触发

linux

服务器设计技术有很多,按使用的协议来分有TCP服务器和UDP服务器。按处理方式来分有循环服务器和并发服务器。

1 循环服务器与并发服务器模型

在网络程序里面,一般来说都是许多客户对应一个服务器,为了处理客户的请求,对服务端的程序就提出了特殊的要求。

目前最常用的服务器模型有:

·循环服务器:服务器在同一时刻只能响应一个客户端的请求

·并发服务器:服

- Oracle数据库查询指令

肆无忌惮_

oracle数据库

20140920

单表查询

-- 查询************************************************************************************************************

-- 使用scott用户登录

-- 查看emp表

desc emp

- ext右下角浮动窗口

知了ing

JavaScriptext

第一种

<!DOCTYPE html PUBLIC "-//W3C//DTD XHTML 1.0 Transitional//EN" "http://www.w3.org/TR/xhtml1/DTD/xhtml1-transitional.dtd">

<html xmlns="http://www.w3.org/1999/

- 浅谈REDIS数据库的键值设计

矮蛋蛋

redis

http://www.cnblogs.com/aidandan/

原文地址:http://www.hoterran.info/redis_kv_design

丰富的数据结构使得redis的设计非常的有趣。不像关系型数据库那样,DEV和DBA需要深度沟通,review每行sql语句,也不像memcached那样,不需要DBA的参与。redis的DBA需要熟悉数据结构,并能了解使用场景。

- maven编译可执行jar包

alleni123

maven

http://stackoverflow.com/questions/574594/how-can-i-create-an-executable-jar-with-dependencies-using-maven

<build>

<plugins>

<plugin>

<artifactId>maven-asse

- 人力资源在现代企业中的作用

百合不是茶

HR 企业管理

//人力资源在在企业中的作用人力资源为什么会存在,人力资源究竟是干什么的 人力资源管理是对管理模式一次大的创新,人力资源兴起的原因有以下点: 工业时代的国际化竞争,现代市场的风险管控等等。所以人力资源 在现代经济竞争中的优势明显的存在,人力资源在集团类公司中存在着 明显的优势(鸿海集团),有一次笔者亲自去体验过红海集团的招聘,只 知道人力资源是管理企业招聘的 当时我被招聘上了,当时给我们培训 的人

- Linux自启动设置详解

bijian1013

linux

linux有自己一套完整的启动体系,抓住了linux启动的脉络,linux的启动过程将不再神秘。

阅读之前建议先看一下附图。

本文中假设inittab中设置的init tree为:

/etc/rc.d/rc0.d

/etc/rc.d/rc1.d

/etc/rc.d/rc2.d

/etc/rc.d/rc3.d

/etc/rc.d/rc4.d

/etc/rc.d/rc5.d

/etc

- Spring Aop Schema实现

bijian1013

javaspringAOP

本例使用的是Spring2.5

1.Aop配置文件spring-aop.xml

<?xml version="1.0" encoding="UTF-8"?>

<beans

xmlns="http://www.springframework.org/schema/beans"

xmln

- 【Gson七】Gson预定义类型适配器

bit1129

gson

Gson提供了丰富的预定义类型适配器,在对象和JSON串之间进行序列化和反序列化时,指定对象和字符串之间的转换方式,

DateTypeAdapter

public final class DateTypeAdapter extends TypeAdapter<Date> {

public static final TypeAdapterFacto

- 【Spark八十八】Spark Streaming累加器操作(updateStateByKey)

bit1129

update

在实时计算的实际应用中,有时除了需要关心一个时间间隔内的数据,有时还可能会对整个实时计算的所有时间间隔内产生的相关数据进行统计。

比如: 对Nginx的access.log实时监控请求404时,有时除了需要统计某个时间间隔内出现的次数,有时还需要统计一整天出现了多少次404,也就是说404监控横跨多个时间间隔。

Spark Streaming的解决方案是累加器,工作原理是,定义

- linux系统下通过shell脚本快速找到哪个进程在写文件

ronin47

一个文件正在被进程写 我想查看这个进程 文件一直在增大 找不到谁在写 使用lsof也没找到

这个问题挺有普遍性的,解决方法应该很多,这里我给大家提个比较直观的方法。

linux下每个文件都会在某个块设备上存放,当然也都有相应的inode, 那么透过vfs.write我们就可以知道谁在不停的写入特定的设备上的inode。

幸运的是systemtap的安装包里带了inodewatch.stp,位

- java-两种方法求第一个最长的可重复子串

bylijinnan

java算法

import java.util.Arrays;

import java.util.Collections;

import java.util.List;

public class MaxPrefix {

public static void main(String[] args) {

String str="abbdabcdabcx";

- Netty源码学习-ServerBootstrap启动及事件处理过程

bylijinnan

javanetty

Netty是采用了Reactor模式的多线程版本,建议先看下面这篇文章了解一下Reactor模式:

http://bylijinnan.iteye.com/blog/1992325

Netty的启动及事件处理的流程,基本上是按照上面这篇文章来走的

文章里面提到的操作,每一步都能在Netty里面找到对应的代码

其中Reactor里面的Acceptor就对应Netty的ServerBo

- servelt filter listener 的生命周期

cngolon

filterlistenerservelt生命周期

1. servlet 当第一次请求一个servlet资源时,servlet容器创建这个servlet实例,并调用他的 init(ServletConfig config)做一些初始化的工作,然后调用它的service方法处理请求。当第二次请求这个servlet资源时,servlet容器就不在创建实例,而是直接调用它的service方法处理请求,也就是说

- jmpopups获取input元素值

ctrain

JavaScript

jmpopups 获取弹出层form表单

首先,我有一个div,里面包含了一个表单,默认是隐藏的,使用jmpopups时,会弹出这个隐藏的div,其实jmpopups是将我们的代码生成一份拷贝。

当我直接获取这个form表单中的文本框时,使用方法:$('#form input[name=test1]').val();这样是获取不到的。

我们必须到jmpopups生成的代码中去查找这个值,$(

- vi查找替换命令详解

daizj

linux正则表达式替换查找vim

一、查找

查找命令

/pattern<Enter> :向下查找pattern匹配字符串

?pattern<Enter>:向上查找pattern匹配字符串

使用了查找命令之后,使用如下两个键快速查找:

n:按照同一方向继续查找

N:按照反方向查找

字符串匹配

pattern是需要匹配的字符串,例如:

1: /abc<En

- 对网站中的js,css文件进行打包

dcj3sjt126com

PHP打包

一,为什么要用smarty进行打包

apache中也有给js,css这样的静态文件进行打包压缩的模块,但是本文所说的不是以这种方式进行的打包,而是和smarty结合的方式来把网站中的js,css文件进行打包。

为什么要进行打包呢,主要目的是为了合理的管理自己的代码 。现在有好多网站,你查看一下网站的源码的话,你会发现网站的头部有大量的JS文件和CSS文件,网站的尾部也有可能有大量的J

- php Yii: 出现undefined offset 或者 undefined index解决方案

dcj3sjt126com

undefined

在开发Yii 时,在程序中定义了如下方式:

if($this->menuoption[2] === 'test'),那么在运行程序时会报:undefined offset:2,这样的错误主要是由于php.ini 里的错误等级太高了,在windows下错误等级

- linux 文件格式(1) sed工具

eksliang

linuxlinux sed工具sed工具linux sed详解

转载请出自出处:

http://eksliang.iteye.com/blog/2106082

简介

sed 是一种在线编辑器,它一次处理一行内容。处理时,把当前处理的行存储在临时缓冲区中,称为“模式空间”(pattern space),接着用sed命令处理缓冲区中的内容,处理完成后,把缓冲区的内容送往屏幕。接着处理下一行,这样不断重复,直到文件末尾

- Android应用程序获取系统权限

gqdy365

android

引用

如何使Android应用程序获取系统权限

第一个方法简单点,不过需要在Android系统源码的环境下用make来编译:

1. 在应用程序的AndroidManifest.xml中的manifest节点

- HoverTree开发日志之验证码

hvt

.netC#asp.nethovertreewebform

HoverTree是一个ASP.NET的开源CMS,目前包含文章系统,图库和留言板功能。代码完全开放,文章内容页生成了静态的HTM页面,留言板提供留言审核功能,文章可以发布HTML源代码,图片上传同时生成高品质缩略图。推出之后得到许多网友的支持,再此表示感谢!留言板不断收到许多有益留言,但同时也有不少广告,因此决定在提交留言页面增加验证码功能。ASP.NET验证码在网上找,如果不是很多,就是特别多

- JSON API:用 JSON 构建 API 的标准指南中文版

justjavac

json

译文地址:https://github.com/justjavac/json-api-zh_CN

如果你和你的团队曾经争论过使用什么方式构建合理 JSON 响应格式, 那么 JSON API 就是你的 anti-bikeshedding 武器。

通过遵循共同的约定,可以提高开发效率,利用更普遍的工具,可以是你更加专注于开发重点:你的程序。

基于 JSON API 的客户端还能够充分利用缓存,

- 数据结构随记_2

lx.asymmetric

数据结构笔记

第三章 栈与队列

一.简答题

1. 在一个循环队列中,队首指针指向队首元素的 前一个 位置。

2.在具有n个单元的循环队列中,队满时共有 n-1 个元素。

3. 向栈中压入元素的操作是先 移动栈顶指针&n

- Linux下的监控工具dstat

网络接口

linux

1) 工具说明dstat是一个用来替换 vmstat,iostat netstat,nfsstat和ifstat这些命令的工具, 是一个全能系统信息统计工具. 与sysstat相比, dstat拥有一个彩色的界面, 在手动观察性能状况时, 数据比较显眼容易观察; 而且dstat支持即时刷新, 譬如输入dstat 3, 即每三秒收集一次, 但最新的数据都会每秒刷新显示. 和sysstat相同的是,

- C 语言初级入门--二维数组和指针

1140566087

二维数组c/c++指针

/*

二维数组的定义和二维数组元素的引用

二维数组的定义:

当数组中的每个元素带有两个下标时,称这样的数组为二维数组;

(逻辑上把数组看成一个具有行和列的表格或一个矩阵);

语法:

类型名 数组名[常量表达式1][常量表达式2]

二维数组的引用:

引用二维数组元素时必须带有两个下标,引用形式如下:

例如:

int a[3][4]; 引用:

- 10点睛Spring4.1-Application Event

wiselyman

application

10.1 Application Event

Spring使用Application Event给bean之间的消息通讯提供了手段

应按照如下部分实现bean之间的消息通讯

继承ApplicationEvent类实现自己的事件

实现继承ApplicationListener接口实现监听事件

使用ApplicationContext发布消息