PYNQ-Z2初识(三)——上手程序

参考铱元素科技2020-03-23PYNQ直播课

文章目录

- 目标

- HLS开发

- Vivado工程

- 导入IP核

- Block Design

- 生成bitstream并导出

- PYNQ上的操作

- 导入PYNQ

- python文件编写

在jupyternotebook 中new一个python文件。

在/pynq/xilinx/pynq/overlays/base目录下有base文件,通常我们需要将这个overlay导入到工程中

from pynq.overlay.base import BaseOverlay

base = BaseOverlay("base.bit)

目标

-

通过HLS定义加法器

写一个C++定义的加法器,转换为RTL语言,并生成IP核 -

overlay的调用

在jupyter notebook中调用我们的加法器ip核,实现加法运算。

HLS开发

打开Vivado HLS

新建一个加法器工程add

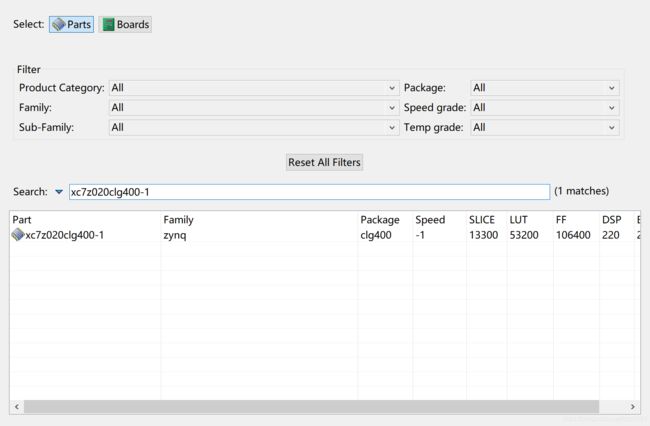

别的都不必管,一路next,就是最后一页的芯片型号要选一下xc7z020clg400-1

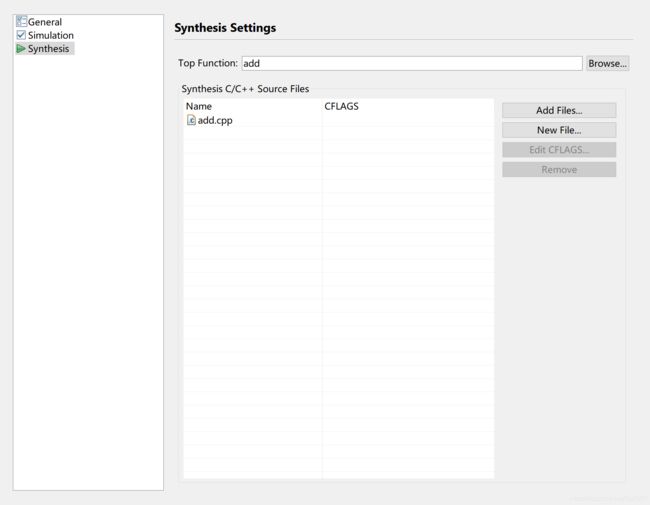

右键左侧目录的source文件夹,add一个名为add.cpp的文件夹,在里面添加一个add函数

void add(int a,int b,int&c)// a和b是两个被操作数,加数和被加数,c是输出结果,取地址。

{

#pragma HLS INTERFACE ap_ctrl_none port = return // ap类型的控制信号定义

// 定义axi类型的接口给a、b、c

#pragma HLS INTERFACE s_axilite port = a

#pragma HLS INTERFACE s_axilite port = b

#pragma HLS INTERFACE s_axilite port = c

c = a + b;//加法操作

}

但是此时还不能进行c综合,需要右键add,点击project setting,在Synthesis中选择add函数作为Top Function

接下来导出RTL为IP核

Vivado工程

完成后打开Vivado,新建工程add

在选择parts/Boards的时候和之前一样输入芯片名称xc7z010clg400-1 (为啥不是选boards呢)

导入IP核

进入settings

打开IP->Repository,将我们HLS工具生成的IP核添加进去

Block Design

点击Create Block Design,在Diagram中添加ip核Add

添加处理系统的IP核ZYNQ,然后Run connection automation

生成bitstream并导出

Synthesis -> Implementation -> Generate Bitstream

不过你直接点Generate Bitstream也可以吼

注意一个问题就是这里需要选择top module,得右键然后Creat HDL Wrapper创建顶层文件

在漫长的等待之后,file>>export>>export block design

PYNQ上的操作

导入PYNQ

通过upload导入.tcl和.bit两个文件

(.tcl文件在project目录,就是export block design的结果)

python文件编写

新建一个python3文件

导入overlay(请务必保证bit文件和tcl文件名字一样)

from pynq import Overlay

overlay = Overlay('/home/xilinx/jupyter_notebooks/HLS_add/design_1.bit')

可以通过overlay?来查看内部包含了什么

ok,有我们的add_0,没问题(我出错了好几次导致这里IP Blocks是none)

接下来创建这个加法器ip

add_ip = overlay.add_0

但是咋往里面写东西呢,就需要SDK工具了

我们先export hardware,再launch SDK

在hdf文件里往下滑,可以找到add的寄存器IP,点击register

搞定,回到我们的程序中,第一个加数的地址是0x10(最后两位就完事了)

写入一个3进去,另一个加数的地址是0x18,写入一个4进去,最后读取一下其相加结果c

add_ip.write(0x10,3)

add_ip.write(0x18,4)

add_ip.read(0x20)

可以得到out的结果7