HDLBits刷题合集—22 Build a circuit from a simulation waveform

HDLBits刷题合集—22 Build a circuit from a simulation waveform

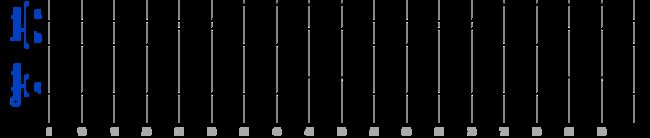

HDLBits-166 Sim/circuit1

Problem Statement

这是一个组合电路。 阅读仿真波形以确定电路的功能,然后实现它。

module top_module (

input a,

input b,

output q );

assign q = a & b;

endmodule

HDLBits-167 Sim/circuit2

Problem Statement

这是一个组合电路。 阅读仿真波形以确定电路的功能,然后实现它。

module top_module (

input a,

input b,

input c,

input d,

output q );//

assign q = (a ^ b) ~^ (c ^ d);

endmodule

HDLBits-168 Sim/circuit3

Problem Statement

这是一个组合电路。 阅读仿真波形以确定电路的功能,然后实现它。

module top_module (

input a,

input b,

input c,

input d,

output q );//

assign q = (a | b) & (c | d);

endmodule

HDLBits-169 Sim/circuit4

Problem Statement

这是一个组合电路。 阅读仿真波形以确定电路的功能,然后实现它。

module top_module (

input a,

input b,

input c,

input d,

output q );//

assign q = b | c;

endmodule

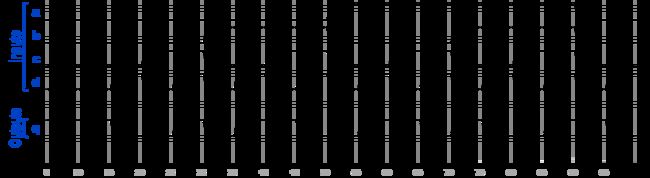

HDLBits-170 Sim/circuit5

Problem Statement

这是一个组合电路。 阅读仿真波形以确定电路的功能,然后实现它。

Simulation 1

module top_module (

input [3:0] a,

input [3:0] b,

input [3:0] c,

input [3:0] d,

input [3:0] e,

output [3:0] q );

always @(*) begin

case (c)

4'H0 : q = b;

4'H1 : q = e;

4'H2 : q = a;

4'H3 : q = d;

default: q = 4'HF;

endcase

end

endmodule

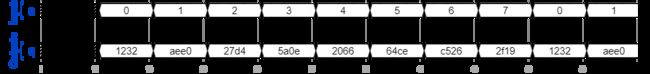

HDLBits-171 Sim/circuit6

Problem Statement

这是一个组合电路。 阅读仿真波形以确定电路的功能,然后实现它。

module top_module (

input [2:0] a,

output [15:0] q );

always @(*) begin

case (a)

3'b0 : q = 16'h1232;

3'b1 : q = 16'haee0;

3'b2 : q = 16'h27d4;

3'b3 : q = 16'h5a0e;

3'b4 : q = 16'h2066;

3'b5 : q = 16'h64ce;

3'b6 : q = 16'hc526;

3'b7 : q = 16'h2f19;

default : q = 16'h0;

endcase

end

endmodule

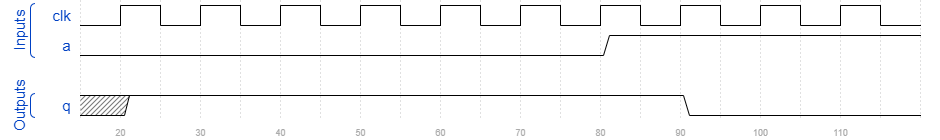

HDLBits-172 Sim/circuit7

Problem Statement

这是一个时序电路。 阅读仿真波形以确定电路的功能,然后实现它。

module top_module (

input clk,

input a,

output q );

always @(posedge clk)

begin

if (a) q <= 1'b0;

else q <= 1'b1;

end

endmodule

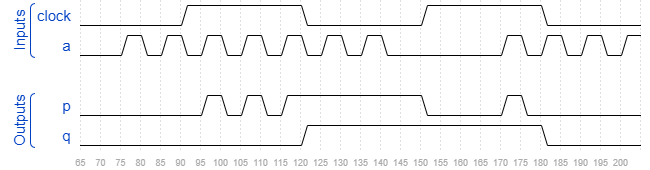

HDLBits-173 Sim/circuit8

Problem Statement

这是一个时序电路。 阅读仿真波形以确定电路的功能,然后实现它。

代码如下:

module top_module (

input clock,

input a,

output p,

output q );

always @(negedge clock) begin

q <= p;

end

always @(*) begin

if (clock) p = a;

else p = p;

end

endmodule

HDLBits-174 Sim/circuit9

Problem Statement

这是一个时序电路。 阅读仿真波形以确定电路的功能,然后实现它。

module top_module (

input clk,

input a,

output [3:0] q );

reg [3:0] q_mid;

always @(posedge clk) begin

if(a)

q_mid <= 4'd4;

else if (q_mid == 4'd6)

q_mid <= 0;

else

q_mid <= q_mid + 4'b1;

end

assign q = q_mid;

endmodule

HDLBits-175 Sim/circuit10

Problem Statement

这是一个时序电路。 该电路由组合逻辑和一位存储器(即一个触发器)组成。 触发器的输出可通过输出状态进行观察。

阅读仿真波形以确定电路的功能,然后实现它。

module top_module (

input clk,

input a,

input b,

output q,

output state );

always @(posedge clk)

begin

if (a == b)

state <= a;

else

state <= state;

end

assign q = (a == b) ? state : ~state;

endmodule

Note

新手一枚,主要分享博客,记录学习过程,后期参考大佬代码或思想会一一列出。欢迎大家批评指正!