HDLBits刷题合集—18 Finite State Machines-4

HDLBits刷题合集—18 Finite State Machines-4

HDLBits-140 Exams/ece241 2013 q8

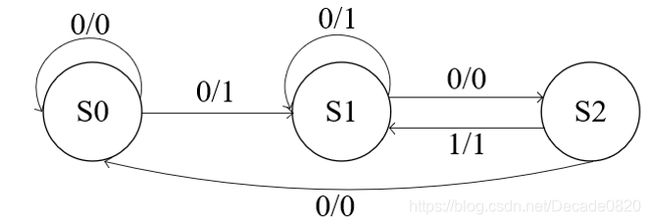

Problem Statement

实现一个Mealy型有限状态机,该状态机可以识别“101”序列,其输入信号命名为x。当检测到“101”序列时,状态机的输出信号将置为逻辑1。该状态机执行低电平有效的异步复位。它可能只有3个状态,而且可以识别重叠的序列。

代码如下:

module top_module (

input clk,

input aresetn, // Asynchronous active-low reset

input x,

output z );

reg [1:0] state, state_next;

parameter S0 = 2'd0, S1 = 2'd1, S2 = 2'd2;

always @(posedge clk or negedge aresetn)

begin

if (!aresetn)

state <= S0;

else

state <= state_next;

end

always @(*)

begin

case (state)

S0 : begin

if (x)

state_next <= S1;

else

state_next <= S0;

end

S1 : begin

if (x)

state_next <= S1;

else

state_next <= S2;

end

S2 : begin

if (x)

state_next <= S1;

else

state_next <= S0;

end

default:

state_next <= S0;

endcase

end

assign z = (state == S2) & (x == 1);

endmodule

HDLBits-141 Exams/ece241 2014 q5a

Problem Statement

你将要设计一个单输入单输出串行的2进制补码器Moore型状态机。 输入(x)是一系列数字(每个时钟周期一个),从数字的最低有效位开始,而输出(Z)是输入的2进制补码。 状态机将接受任意长度的输入数字。该电路需要异步复位。 转换在reset低电平时开始,并在reset高电平时停止。

module top_module (

input clk,

input areset,

input x,

output z

);

parameter A=2'b00, B=2'b01, C=2'b10, D=2'b11;

reg [1:0] state, state_next;

always @(posedge clk or posedge areset)

begin

if (areset)

state <= A;

else

state <= state_next;

end

always @(state or x)

begin

case (state)

A: begin

if (x) state_next <= B;

else state_next <= A;

end

B: begin

if (x) state_next <= C;

else state_next <= B;

end

C: begin

if (x) state_next <= C;

else state_next <= B;

end

default: state_next <= A;

endcase

end

assign z = (state == B);

endmodule

HDLBits-142 Exams/ece241 2014 q5b

Problem Statement

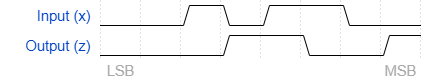

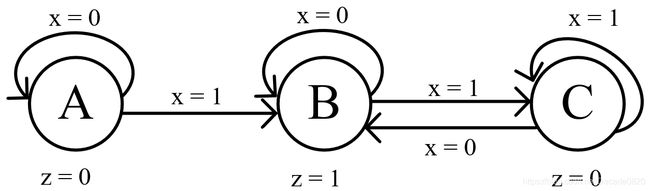

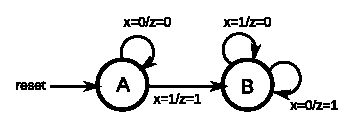

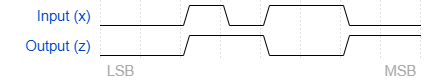

下图是2进制补码器在Mealy型状态机上的实现。 使用独热码编码实现。

状态转换图:

波形图:

代码如下:

module top_module (

input clk,

input areset,

input x,

output z

);

parameter A=2'd1, B=2'd2;

reg [1:0] state,state_next;

always @(posedge clk or posedge areset)

begin

if (areset)

state <= A;

else

state <= state_next;

end

always @(*) begin

case (state)

A: begin

if (x)

state_next <= B;

else

state_next <= A;

end

B: begin

state_next <= B;

end

default: begin

state_next <= A;

end

endcase

end

assign z = ((state == A) & (x == 1)) | ((state == B) & (x == 0));

endmodule

HDLBits-143 Exams/2014 q3fsm

Problem Statement

考虑一个输入为s和w的有限状态机。 假定FSM以复位状态A开始,如下所示。 只要s = 0,FSM就会保持状态A,而当s = 1时,FSM会进入状态B。一旦进入状态B,FSM就会在接下来的三个时钟周期中检查输入w的值。 如果恰好在这些时钟周期中的两个时钟周期中w = 1,则FSM必须在下一个时钟周期中将输出z设置为1。 否则z必须为0。FSM在接下来的三个时钟周期中继续检查w,依此类推。 下面的时序图说明了不同w值所需的z值。

使用尽可能少的状态。 请注意,s输入仅在状态A中使用,因此只需要考虑w输入。

module top_module (

input clk,

input reset, // Synchronous reset

input s,

input w,

output z

);

parameter A=0, B=1, C=2, D=3, E=4, F=5, H=6, L=7;

reg [2:0] state, state_next;

always @(*) begin

case (state)

A : begin

if (s) state_next = B;

else state_next = A;

end

B : begin

if (w) state_next = D;

else state_next = C;

end

C : begin

if (w) state_next = F;

else state_next = E;

end

D : begin

if (w) state_next = H;

else state_next = F;

end

E : begin

state_next = B;

end

F : begin

if (w) state_next = L;

else state_next = B;

end

H : begin

if (w) state_next =B;

else state_next = L;

end

L : begin

if (w) state_next = D;

else state_next = C;

end

endcase

end

always @(posedge clk)

begin

if (reset) state <= A;

else state <= state_next;

end

assign z = (state == L);

endmodule

HDLBits-144 Exams/2014 q3bfsm

Problem Statement

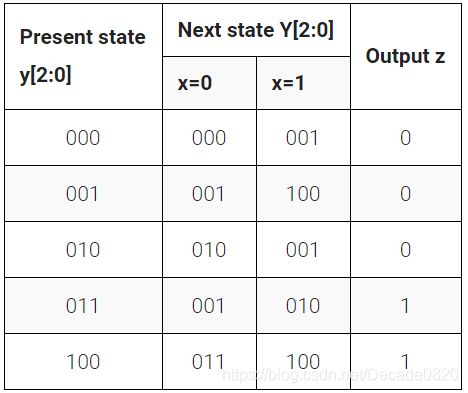

给定如下所示的状态分配表,实现该有限状态机。 重置应将FSM重置为000状态。

module top_module (

input clk,

input reset, // Synchronous reset

input x,

output z

);

parameter S0=0, S1=1, S2=2, S3=3, S4=4;

reg [2:0] state, state_next;

always @(*) begin

case (state)

S0 : begin

if (x) state_next = S1;

else state_next = S0;

end

S1 : begin

if (x) state_next = S4;

else state_next = S1;

end

S2 : begin

if (x) state_next = S1;

else state_next = S2;

end

S3 : begin

if (x) state_next = S2;

else state_next = S1;

end

S4 : begin

if (x) state_next = S4;

else state_next = S3;

end

default: begin

state_next = S0;

end

endcase

end

always @(posedge clk)

begin

if (reset) state <= S0;

else state <= state_next;

end

assign z = (state == S3) | (state == S4);

endmodule

HDLBits-145 Exams/2014 q3c

Problem Statement

给定如下所示的状态分配表,请实现逻辑功能Y[0]和z。

module top_module (

input clk,

input [2:0] y,

input x,

output Y0,

output z

);

parameter S0=3'b000, S1=3'b001, S2=3'b010, S3=3'b011, S4=3'b100;

reg [2:0] state_next;

always @(*) begin

case (y)

S0 : begin

if (x) state_next = S1;

else state_next = S0;

end

S1 : begin

if (x) state_next = S4;

else state_next = S1;

end

S2 : begin

if (x) state_next = S1;

else state_next = S2;

end

S3 : begin

if (x) state_next = S2;

else state_next = S1;

end

S4 : begin

if (x) state_next = S4;

else state_next = S3;

end

default: begin

state_next = S0;

end

endcase

end

assign z = (y == S3) | (y == S4);

assign Y0 = state_next[0];

endmodule

Note

新手一枚,主要分享博客,记录学习过程,后期参考大佬代码或思想会一一列出。欢迎大家批评指正!