怎么独立使用Modelsim进行工程仿真

原帖:http://www.cnblogs.com/yuphone/archive/2010/08/30/1812932.html

转贴: 天马行空W https://www.cnblogs.com/woshitianma/archive/2012/11/30/Questasim.html

感谢文档:艾米电子

本人一直用的都是ISE自带的仿真器ISIM进行仿真。后因一篇modulsim的DDR3仿真,带入了moduisim的学习。经过亲身时间以后,觉得modulsim对于笔者来说,并不是很舒服,可能是ISIM用的多了吧。但是大致思维都是一样的。

相信很多小伙伴怎么在modulsim中添加XILINX的库,还是一脸迷茫。笔者会在有空的时候,附上此教程。各位看官,可以先根据上一帖自行安装modulsim。等不及的小伙伴只能自己去百度查啦!

1 设计流程

使用Modulesim仿真的基本流程为

2 开始仿真工程建立

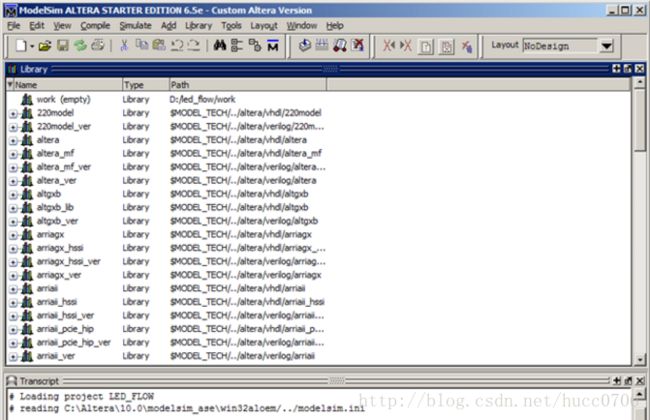

2.1 首先打开Modulesim

打开后的界面如下图所示

图2.2 Modulesim界面

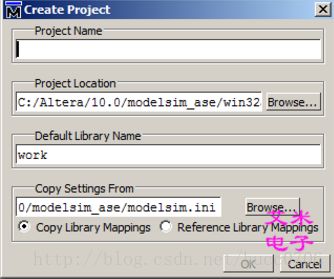

1-选择择File>New>Preject创建一个新工程。打开的Create Project对话框窗口,可以指定工程的名称、路径和缺省库名称。一般情况下,设定Default Library Name为work。指定的名称用于创建一个位于工程文件夹内的工作库子文件夹。该对话框如图2.2所示,此外还允许通过选择.ini文件来映射库设置,或者将其直接拷贝至工程中。

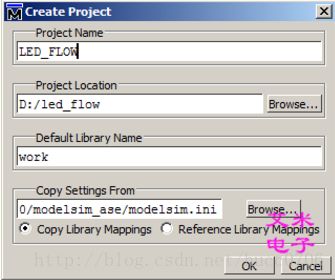

图2.4建立工程project : ssram

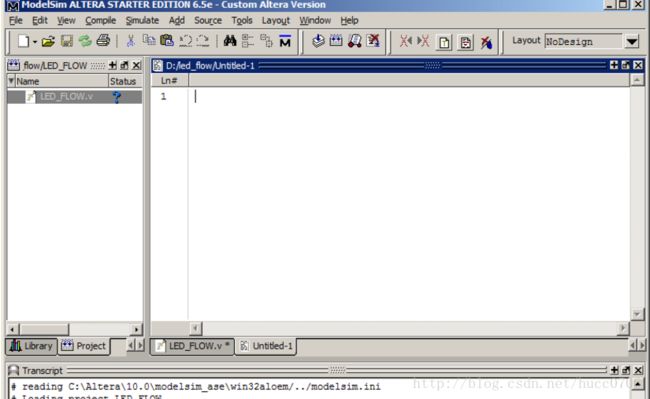

2. 按照图2.3所示,设置Project Name为LED_FLOW,Project Location为D:/led_flow

当单击OK按钮后,在主体窗口的下方将出现Project标签,如图2.4所示。

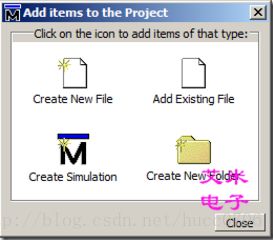

3. 之后,将出现Add Items to the Project的对话框,如图2.5所示。

在这一对话框里,我们看到在Add Items to the Project对话框中,包括以下选项:

- Create New File——使用源文件编辑器创建一个新的Verilog、VHDL、TCL或文本文件

- Add Existing File——添加一个已存在的文件

- Create Simulation——创建指定源文件和仿真选项的仿真配置

- Create New Folder——创建一个新的组织文件夹

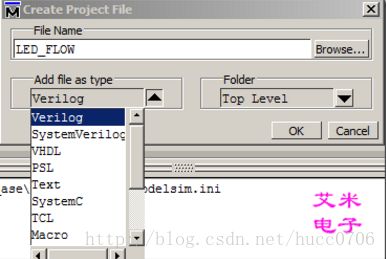

1.单击Create New File,打开如下图所示的对话框:

图2.6 创建工程文件夹

2. 输入文件名称:LED_FLOW,然后选择文件类型为Verilog。

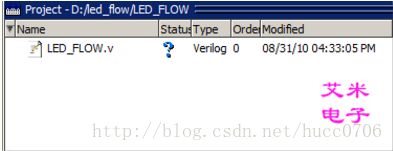

3. 单击OK,关闭本对话框。新的工程文件将会在工程窗口显示。单击Close,以关闭Add Items to the Project。

单击选中project栏中ssram_tst文件,右键选择属性properities,可以看到文件所在位置正是我们新建的文件夹的位置。

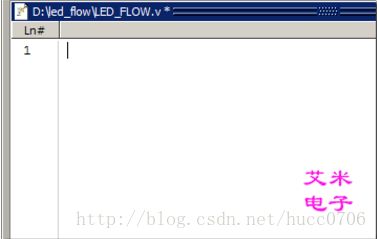

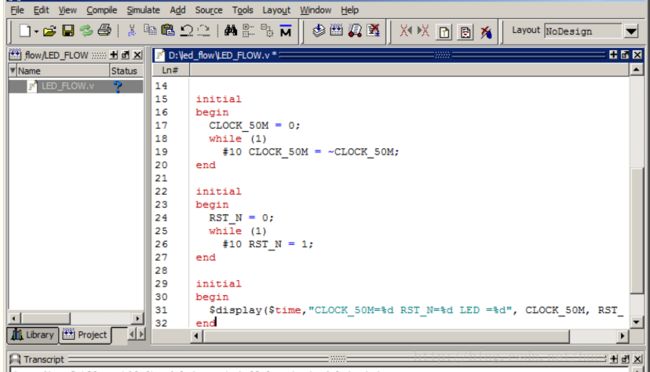

4. 双击打开LED_FLOW.v文件(注意:若是Verilog文件已经关联了其他的文本编辑器,则双击后在关联的文本编辑器中打开)。

右侧,便是代码输入窗口。在这一窗口中输入的是testbench代码,用于module的测试。

在LED_FLOW.v输入下面的测试平台代码:

在LED_FLOW.v输入下面的测试平台代码:

|

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

|

`

timescale

1ns/1ns

module

LED_FLOW;

reg

CLOCK_50M;

reg

RST_N;

wire

[9:0] LED;

led led_inst

(

.clk_50M(CLOCK_50M),

.reset_n(RST_n),

.led(LED)

);

initial

begin

CLOCK_50M = 0;

while

(1)

#10 CLOCK_50M = ~CLOCK_50M;

end

initial

begin

RST_N = 0;

while

(1)

#10 RST_N = 1;

end

initial

begin

$

display

($

time

,

"CLOCK_50M=%d RST_N=%d LED =%d"

, CLOCK_50M, RST_N, LED);

end

endmodule

|

录入完代码后,单击Save。出现下面的状态。

在sava后,右侧的代码区关键词变成了红色//在例化的时候最好不用i1作为例化名,这样Modelsim可能不认识,起一个另外的名字最好。

其是本质和模块的调用是一致的,就是用tesrbench的代码去调用例化在testbench中的待测试Module。

声明好自己的testbench,reg和wire变量,然后再例化好待测试module,再编写测试代码,这样就可以了

5. 选择File>New>Source>Verilog,创建新的Verilog文件,如图2.10所示。

6. 录入下面的代码,录入画面如图2.12 所示。

|

1

2

3

4

5

6

7

8

9

|

`

timescale

1ns/1ns

module

led(

input

clk_50M,

// System clock 50MHz

input

reset_n,

// System reset

output

reg

[9:0] led

// led

);

reg

[13:0] counter = 0;

reg

[3:0] state = 0;

|

|

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

2

|

always

@ (

posedge

clk_50M,

negedge

reset_n)

if

(!reset_n)

counter <= 0;

else

counter <= counter +

1'b1

;

always

@ (

posedge

counter[13])

if

(!reset_n)

state <= 0;

else

begin

if

(state ==

4'b1001

)

state <= 0;

else

state <= state +

1'b1

;

end

always

@ (

posedge

clk_50M,

negedge

reset_n)

if

(!reset_n)

led <= 0;

else

begin

case

(state)

4'b0000

: led <=

10'b00000_00001

;

4'b0001

: led <=

10'b00000_00010

;

4'b0010

: led <=

10'b00000_00100

;

4'b0011

: led <=

10'b00000_01000

;

4'b0100

: led <=

10'b00000_10000

;

4'b0101

: led <=

10'b00001_00000

;

4'b0110

: led <=

10'b00010_00000

;

4'b0111

: led <=

10'b00100_00000

;

4'b1000

: led <=

10'b01000_00000

;

4'b1001

: led <=

10'b10000_00000

;

default

: led <=

10'b00000_00001

;

endcase

end

endmodule

|

7. 选择File>Save,输入文件名:led.v,单击Save,如图2.13所示。

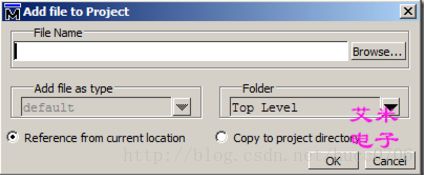

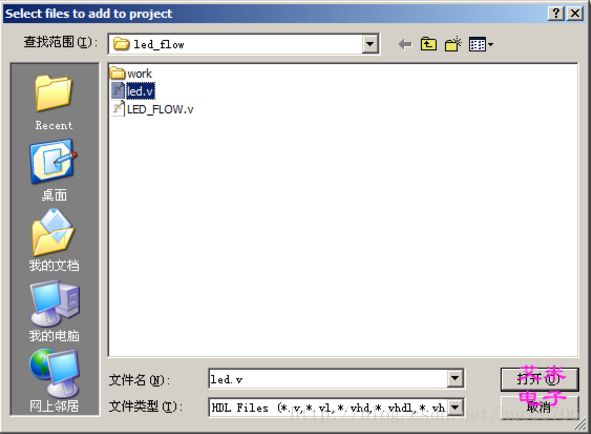

8. 选择Project>Add to Project>Existing File,如图2.14所示

9. 单击Browse,选择ssram.v,如图2.13 所示。

10. 单击打开,在Add file to the project窗口,单击OK

2.3 编译文件

在Project标签下的Status列的问号,表示文件尚未编译进工程,或者在最后编译前,源文件有所改动。欲编译文件,选择Compile

1. 倘若此处没有错误,编译成功的消息,就会在Transcript窗口如图2.6所示。

#

# reading modelsim.ini

# reading D:\questasim_10.0c\win32/../modelsim.ini

# Loading project ssram

# Compile of ssram_tst.v was successful.

# Compile of ssram.v was successful.

# 2 compiles, 0 failed with no errors.

|

编译成功!

3 仿真工程

3.1 开始仿真

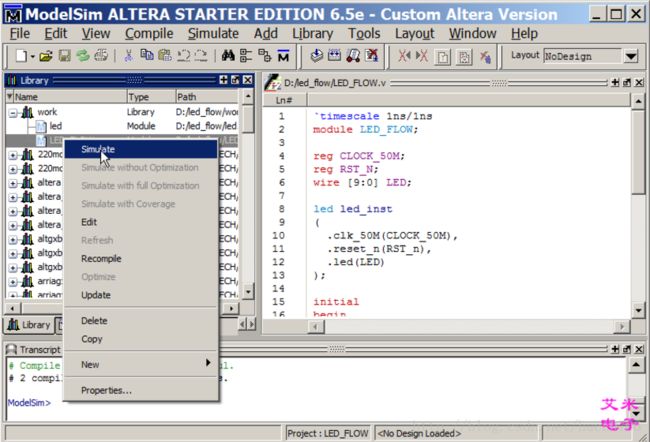

1. 单击Library图标,选择work,单击+以展开选项,然后选择LED_FLOW。单击右键,选择编译,如图3.1所示

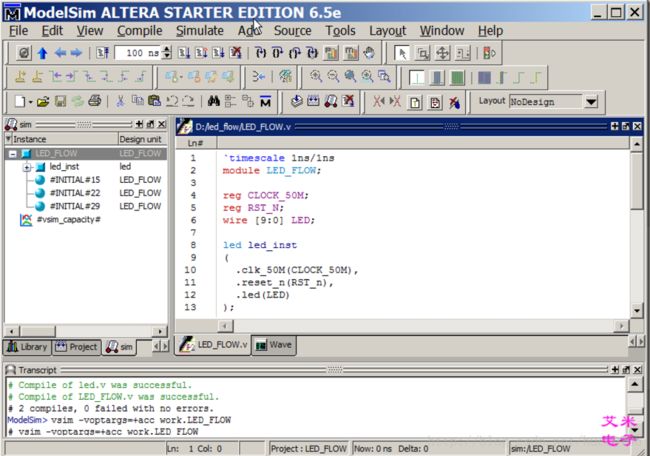

2. 单击Simulate,到达图3.2所示画面。

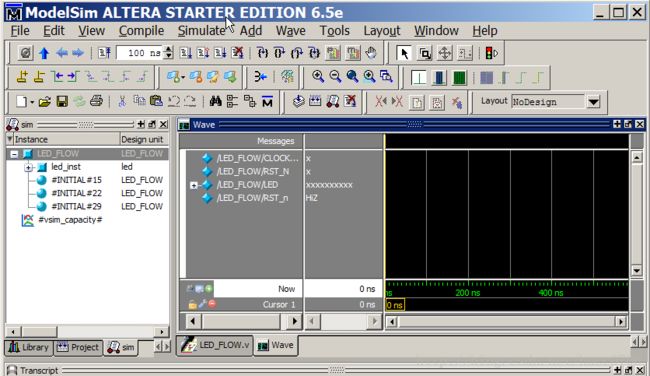

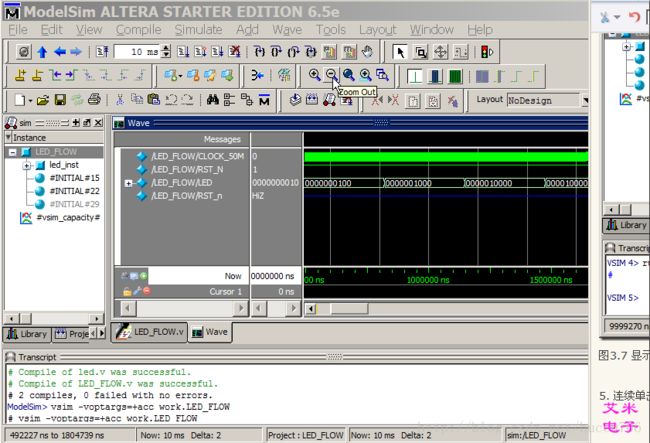

4. 在图3.2中,单击LED_FLOW,单击右键,然后选择Add>To Wave>All Items in region,然后单击左键。出现图3.3所示画面。

3.2 仿真设置

1. 完成上述最后一步后,波形窗口出现。

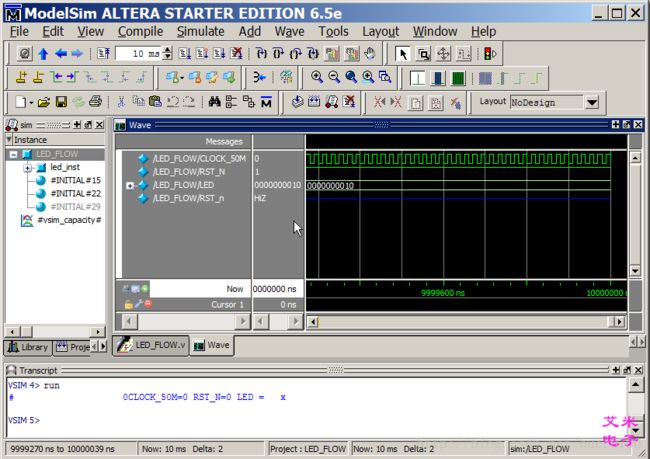

2. 在Run Length列输入仿真时间长度为1000ms,如图3.5所示。

3. 单击Run按钮进行仿真,如图所示。

4. 运行若干秒后,将会如图3.9所示的仿真结果。

5. 连续单击Zoom IN/Out图标,可查看仿真的完整波形。

通过放大/缩小波形,可以观察到ssram的地址值在保持变化,即ssram的时序效果。若将其移植到Quartus II中,适当配置后,经过综合、时序分析、引脚分配、配置及下载等,即可实现ssram读取比较正误的效果。

参考

1. Terasic.DE2_115_v.1.0_CDROM\DE2_115_tutorials\modelsim_tutorial.pdf