- VCS简介

XtremeDV

VCS快速实战指南

1.2.1关于VCSVCS是VerilogCompiledSimulator的缩写。VCSMX®是一个编译型的代码仿真器。它使你能够分析,编译和仿真Verilog,VHDL,混合HDL,SystemVerilog,OpenVera和SystemC描述的设计。它还为您提供了一系列仿真和调试功能,以验证您的设计。这些功能提供了源码调试和仿真结果查看功能。vcs提供了一系列的feature,如下图:业界

- vcs 入门

hemmingway

Xilinx/FPGA

synopsysvcs软件是仿真和验证的软件,必须掌握。vcs即verilogcompilesimulator支持verilog,systemVerilog,openvera,systemC等语言,同时也有代码覆盖率检测等功能。可以合第三方软件集合使用,例如Vera,Debussy,Specman等等。在linux下调用vcs,需要设置相应的环境变量。1、学习vcs最好的资料肯定是官方的说明书,安

- Xilinx Vivado的RTL分析(RTL analysis)、综合(synthesis)和实现

2401_84185145

程序员fpga开发

理论上,FPGA从编程到下载实现预期功能的过程最少仅需要上述7个步骤中的4、5、6和7,即RTL分析、综合、实现和下载。其中的RTL分析、综合、实现的具体含义和区别又是什么?2、RTL分析(RTLanalysis)一般来讲,通常的设计输入都是Verilog、VHDL或者SystemVerilog等硬件描述语言HDL编写的文件,RTL分析这一步就是将HDL语言转化成逻辑电路图的过程。比如HDL语言描

- System Verilog学习笔记(十二)——数组(2)

颖子爱学习

SystemVerilog学习笔记学习笔记

SystemVerilog学习笔记(十二)——数组(2)动态数组在编译时不会为其定制尺寸,而是在仿真运行时来确定动态数组一开始为空,需要使用new[]来为其分配空间声明方式intdyn[],d2[];//声明了两个动态数组initialbegindyn=new[5];//包含5个元素foreach(dyn[j])dyn[j]=j;//初始化元素d2=dyn;//拷贝数组dyn.delete();/

- fpga 需要掌握哪些基础知识?

宸极FPGA_IC

fpga开发fpga硬件工程嵌入式硬件javastm32

个人根据自己的一些心得总结一下fpga需要掌握的基础知识,希望对你有帮助。1、数电(必须掌握的基础),然后进阶学模电,2、掌握HDL(verilog或VHDL)一般建议先学verilog,然后可以学SystemVerilog和VHDL。3、掌握FPGA设计流程/原理(推荐教材:FPGA权威指南、AlteraFPGA/CPLD设计、IP核芯志-数字逻辑设计思想、静态时序分析、嵌入式逻辑分析仪等)。4

- vscode开发FPGA(0)--windows平台搭建

zidan1412

FPGAvscode编辑器

一、从官网下载安装VScodeDownloadVisualStudioCode-Mac,Linux,Windows二、安装配置插件1.安装Chinese(simplified)中文汉化包2.安装Verilog-HDL/systemVerilog插件(支持verilog语法)3.配置CTagsSupport插件(支持代码跳转)1)在github下载universalctags最新版本Release2

- 数字芯片验证入门

凳子花❀

验证数字IC设计Veriloguvmsystemverilog数字芯片验证

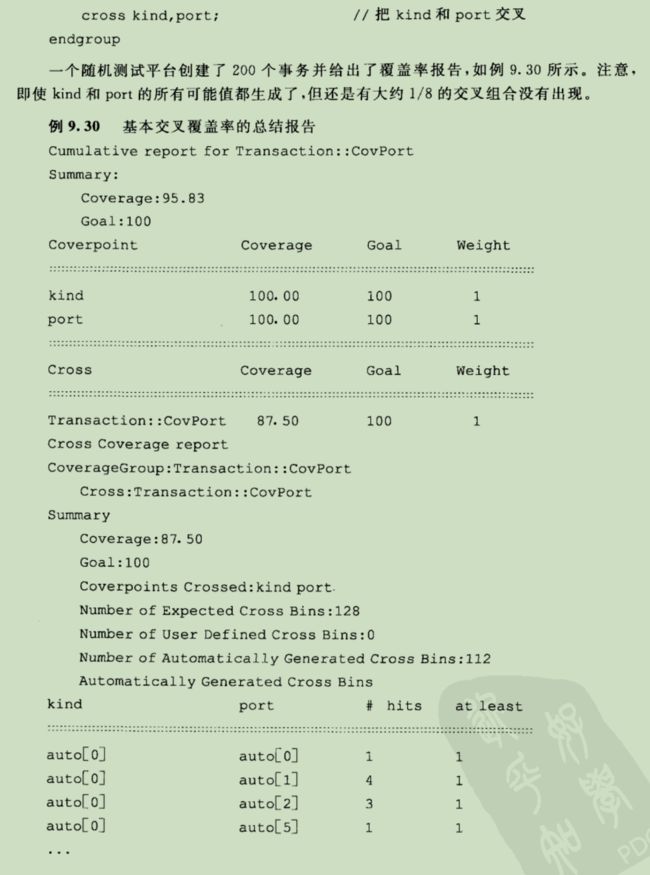

文章目录数字芯片验证入门1.验证那些事2.芯片验证系列——Testpoints分解3.芯片验证系列——验证计划4.关于芯片验证中写testcase的一些想法SystemVerilog1.随机化策略——随机变量rand、约束constraint、权重dist、随机数产生示例2.SV--Coverage覆盖率3.SystemVerilogTutorial4.foreach5.多线程数字芯片验证入门最近

- 【芯片设计- RTL 数字逻辑设计入门 11.1 -- 状态机实现 移位运算与乘法 1】

CodingCos

芯片设计RTL数字逻辑设计扫盲fpga开发

文章目录移位运算与乘法状态机简介SystemVerilog中的测试平台VCS波形仿真阻塞赋值和非阻塞赋值有限状态机(FSM)与无限状态机的区别本篇文章接着上篇文章【芯片设计-RTL数字逻辑设计入门11–移位运算与乘法】继续介绍,这里使用状态机来实现。移位运算与乘法已知d为一个8位数,请在每个时钟周期分别输出该数乘1/3/7/8,并输出一个信号通知此时刻输入的d有效(d给出的信号的上升沿表示写入有效

- systemverilog 宏定义 `define

hh199203

systemverilogsystemverilog宏定义参数传递

文章目录前言1标准中关于`define宏的介绍1.1特殊符号`"1.2特殊符号\`\`"1.3特殊符号``2带参数的宏`define2.1带参数宏的使用方法及其存在的问题2.2解决宏定义变量传参的方法总结前言本文主要记录一下systemverilog中`define宏定义的使用,主要介绍带参数的宏传递方法。1标准中关于`define宏的介绍在《SystemVerilog_3.1a》标准中,关于`d

- 如何理解派生类的构造函数

hh199203

systemverilog构造函数new

文章目录前言一、派生类的构造函数二、派生类的构造函数举例总结前言在class中,有的时候有构造函数new,有的时候又没有构造函数new,本文主要记录一下,派生类的构造函数的执行过程,帮助更好的理解class的构造函数。一、派生类的构造函数当派生类中没有构造函数时,VCS会自动插入一个构造函数new,并执行其父类中的构造函数super.new();当派生类中有构造函数时,systemverilog期

- SystemVerilog约束随机(二)

hh199203

systemverilogsystemverilog随机约束

文章目录前言一、SystemVerilog约束随机1.1集合操作setmembership1.2权重约束weightedconstraints1.3队列约束arrayconstranint1.4条件约束orderconstraints1.5等价约束equivalenceconstraints1.6顺序约束solverorder总结前言这里主要记录一下systemverilog中的一些约束,包括:集

- Vivado编译介绍

cckkppll

fpga开发

Vivado编译介绍合成是将寄存器传输级别(RTL)指定的设计转换为门级表示。AMDVivado™合成是定时驱动的,并针对内存进行优化使用和性能。Vivado合成支持以下的可合成子集:•SystemVerilog:IEEE标准SystemVerilog统一硬件设计规范,以及验证语言(IEEEStd1800-2012)•Verilog:IEEEVerilog硬件描述语言标准(IEEEStd1364-

- 【数字IC精品文章收录】近500篇文章-学习路线-基础知识-接口-总线-脚本语言-芯片求职-安全-EDA-工具-低功耗设计-Verilog-低功耗-STA-设计-验证-FPGA-架构-AMBA-书籍-

程序员负总裁

学习安全fpga开发

数字IC全站文章索引demo版(建议收藏慢慢看)*一、项目说明*1.1索引目的1.2收录原则1.3投稿方式1.4版本迭代二、数字IC学习路线三、通用技能篇*3.1数字电路3.2硬件描述语言(Verilog)3.3linux操作系统3.4C语言3.5微机原理3.6汇编语言3.7计算机组成原理3.8计算机体系架构3.9STA静态时序分析3.10SystemVerilog3.11UVM3.12SVA3.

- SystemVerilog中数组内置函数sum()的一个注意点

谷公子的藏经阁

SystemVerilogSystemverilog数组内置函数芯片设计芯片验证UVM

Systemverilog内置了数组求和运算方法(sum()),将数组的所有元素累加起来,返回一个最终值。在使用时要注意数组类型的位宽,通常情况下,如果你将一组单bit的值加起来,Systemverilog会使用足够的精度来确保不丢失任何bit的值。但是数组内置方法sum()使用的是数组类型的位宽,因此,如果你直接使用sum()去算单bit类型的数组,那么最终结果还是单bit,这可能不是你所期望的

- “OVL断言“和“assert 断言“有什么区别和联系

禅空心已寂

uvmIC验证前端OVLassert

目录区别:1.OVL断言:2.SystemVerilog`assert`断言:3.设计目的:4.语法:5.特定功能:联系:1.都属于基于断言的验证:2.都用于仿真验证:3.都可用于捕获设计中的问题:OVL(OpenVerificationLibrary)断言和SystemVerilog的`assert`断言都是在验证中用于描述设计性质和约束的工具,都是基于断言的验证方法,但它们有一些关键的区别和联

- $hdl_xmr_force,$value$plusargs

禅空心已寂

前端uvmsystemverilog系统函数

1、$hdl_xmr_force:tasktriggerreset();$hdl_xmr_force("rkvtimertb.apbrstn","0");//rkvtimertb.apbrstn<=0;#20ns;$hdl_xmr_force("rkvtimertb.apbrstn",“1");//rkvtimertb.apbrstn<=1;endtask在SystemVerilog中,`$hdl

- Barrel Shifter RTL Combinational Circuit——桶移位寄存器SystemVerilog实现

疯狂的泰码君

SystemVerilogSystemVerilog

在本博客中,将围绕许多设计中存在的非常有用的电路(桶形移位器电路)设计电路。将从最简单的方法开始实现固定位宽字的单向旋转桶形移位器,最后设计一个具有可参数化字宽的多功能双向桶形移位器电路。BarrelShifter桶形移位器是一种数字电路,可以将数据字移位指定位数,而不使用任何顺序逻辑,仅使用纯组合逻辑。它有一个控制输入,指定它移动的位数。桶移位器类似于移位寄存器(多位),不同之处在于寄存器的移位

- 数字电路设计——加法器

爱寂寞的时光

电子技术计算机体系结构算法硬件工程嵌入式硬件

数字电路设计——加法器半加器半加器只有两个一位宽的输入aaa和bbb,输出a+ba+ba+b所产生的本位和sumsumsum和进位coutcoutcout。组合逻辑为:S=A⊕B,Cout=ABS=A\oplusB,Cout=ABS=A⊕B,Cout=AB真值表和原理图符合为:SystemVerilog实现代码:modulehadder(inputlogica,inputlogicb,output

- 【system verilog】SV Assertion 断言

飓风_数字IC验证

systemverilog硬件工程

SystemVerilogAssertion断言总结SV断言是什么?有什么用?SV断言是什么?SV断言有什么用?SV断言怎么用?SV断言语法即时断言与并发断言即时断言并发断言序列sequence边缘表达式时钟周期延迟属性property时钟定义禁止属性执行块蕴含操作后续算子固定延迟的蕴含使用序列作为先行算子的蕴含嵌套的蕴含在蕴含中使用ifelse时序窗口重叠的时序窗口语法之ended结构$past

- 【system verilog】Mailboxes

飓风_数字IC验证

systemverilog开发语言

mailbox的功能:Mailboxes是一种在进程之间交换消息的机制。数据可以通过一个进程发送到Mailboxes,然后由另一个进程获取。mailbox中可以放的数据:数据可以是任何有效的systemVerilog数据类型,包括类class数据类型。非参数化Mailboxes是无类型的,即单个Mailboxes可以发送和接收不同类型的数据。SystemVerilog提供以下使用邮箱的方法:Mai

- 格式化verilog/systemverilog代码插件

weixin_30652897

开发工具

1.插件sourcecodehttps://github.com/vhda/verilog_systemverilog.vim2.安装插件解压后copyverilog_systemverilog.vim文件夹到:~/.vim/bundleNote:前提是安装了pathogen插件管理器,安装请参考:https://www.cnblogs.com/bky-lxin/p/11607146.html3.

- SystemVerilog验证测试平台:2.2章节:定宽数组

一只迷茫的小狗

Systemverilogsystemverilog

2.2定宽数组相比于Verilog1995中的一维定宽数组,Systemverilog提供了更加多样的数组类型,功能上也大大增强。2.2.1定宽数组的声明和初始化Verilog要求在声明中必须给出数组的上下界。因为几乎所有数组都使用0作为索引下界,所以Systemverilog允许只给出数组宽度的便捷声明方式,跟C语言类似。例2.4定宽数组的声明intlo_hi[0:15];//16个整数[0].

- systemverilog中对文件的操作方法

ohuo666

systemverilog

1.打开文件和关闭文件利用$fopen()函数打开文件,打开一个名为filename的文件,filename里可包含文件路径,同时filename为字符串类型,type也为字符串类型,决定对文件的操作方式,可包括如下的操作类型,默认方式为以“w”或“wb”方式打开。注意"w","wb","w+","w+b","wb+"打开文件将会清空文件原有数据。其中“b”用于区别文本文件和二进制文件。如果一个文

- IEEE SystemVerilog Chapter15:Interprocess synchronization and communication

一只迷茫的小狗

Systemverilogsystemverilog

15.2Overview高级且易于使用的同步和通信机制对于控制用于建模复杂系统或高反应性测试台的动态过程之间发生的各种交互至关重要。基本的同步机制是命名的事件类型,以及事件触发器和事件控制结构(即->和@)。这种类型的控件仅限于静态对象。它足以在硬件级别和简单系统级别进行同步,但不能满足高度动态、反应性测试台的需求。SystemVerilog还提供了一套强大且易于使用的同步和通信机制,这些机制可以

- systemverilog_用于SystemVerilog和Verilog文件的Eclipse插件

diluan6799

javaeclipsemavenlinux大数据

systemverilogSVEditor团队针对SystemVerilog和Verilog文件发布了其基于Eclipse的开发环境插件的0.1.1版。它基于Java,具有语法着色,结构显示和内容辅助功能。SVEditor是根据EclipsePublicLicense发布的。可以从SourceForge下载。翻译自:https://jaxenter.com/eclipse-plugin-for-s

- systemverilog/verilog文件操作

一只迷茫的小狗

Systemverilogverilogsystemverilog

1、Verilog文件操作Verilog具有系统任务和功能,可以打开文件、将值输出到文件、从文件中读取值并加载到其他变量和关闭文件。1.1、Verilog文件操作1.1.1、打开和关闭文件moduletb;//声明一个变量存储filehandlerintegerfd;initialbegin//以写权限打开一个文件名为"my_file.txt"的新文件,并将文件柄指针存储在变量"fd"中fd=$f

- UVM的guideline

谷公子的藏经阁

UVMMentor指导手册systemverilog芯片

UVM库是类的集合,它通过提供如何使用SystemVerilog中的功能结构,使SystemVerilog语言使用起来更为通用顺畅。然而,在许多情况下,UVM提供多种机制来完成相同的工作。因此,Mentor提供了一些使用UVM的建议,意在帮忙大家更有效率的使用UVM。1.在package里定义class,其它package需要的话,采用import的方式导入类。不要使用include的方式将同一个

- Verilog 和 System Verilog 的区别

疯狂的泰码君

FPGAVerilogVerilog

当谈到VLSI设计和数字电路建模时,verilog和systemverilog是两种常用的硬件描述语言。这些HDL在VLSI设计中用于描述电子电路的行为和结构。它们都广泛应用于半导体行业来设计和实现集成电路(IC)。它们是设计和模拟复杂数字系统的强大工具。在本文中,我们将深入研究这两种HDL之间的主要区别,阐明它们在VLSI设计领域的特性和功能。VerilogVerilog是一种硬件描述语言,几十

- systemverilog-数据类型(logic、数组、队列、结构体、枚举类、字符串)

zer0hz

systemverilogsystemverilog

文章目录logicbit数组数组的定义定宽数组多维数组合并数组常量数组动态数组关联数组数组操作数组缩减方法数组随机选择一个元素数组的定位队列定义和使用结构体结构体的定义非压缩结构体和压缩结构体

- SystemVerilog学习之路(5)— 结构体、枚举类型和字符串

Willliam_william

SystemVeriloggolangc语言数据结构

SystemVerilog学习之路(5)—结构体、枚举类型和字符串一、前言在SystemVerilog中可以和C语言一样使用typedef来创建新的类型,这样通过和结构体的配合便可以自定义我们想要的数据类型了。二、结构体类型在SystemVerilog中可以使用struct创建结构体,不过struct的功能少,它只是一个数据的集合,其通常的使用方式是将若干相关的变量组合到一个struct结构定义中

- ztree设置禁用节点

3213213333332132

JavaScriptztreejsonsetDisabledNodeAjax

ztree设置禁用节点的时候注意,当使用ajax后台请求数据,必须要设置为同步获取数据,否者会获取不到节点对象,导致设置禁用没有效果。

$(function(){

showTree();

setDisabledNode();

});

- JVM patch by Taobao

bookjovi

javaHotSpot

在网上无意中看到淘宝提交的hotspot patch,共四个,有意思,记录一下。

7050685:jsdbproc64.sh has a typo in the package name

7058036:FieldsAllocationStyle=2 does not work in 32-bit VM

7060619:C1 should respect inline and

- 将session存储到数据库中

dcj3sjt126com

sqlPHPsession

CREATE TABLE sessions (

id CHAR(32) NOT NULL,

data TEXT,

last_accessed TIMESTAMP NOT NULL,

PRIMARY KEY (id)

);

<?php

/**

* Created by PhpStorm.

* User: michaeldu

* Date

- Vector

171815164

vector

public Vector<CartProduct> delCart(Vector<CartProduct> cart, String id) {

for (int i = 0; i < cart.size(); i++) {

if (cart.get(i).getId().equals(id)) {

cart.remove(i);

- 各连接池配置参数比较

g21121

连接池

排版真心费劲,大家凑合看下吧,见谅~

Druid

DBCP

C3P0

Proxool

数据库用户名称 Username Username User

数据库密码 Password Password Password

驱动名

- [简单]mybatis insert语句添加动态字段

53873039oycg

mybatis

mysql数据库,id自增,配置如下:

<insert id="saveTestTb" useGeneratedKeys="true" keyProperty="id"

parameterType=&

- struts2拦截器配置

云端月影

struts2拦截器

struts2拦截器interceptor的三种配置方法

方法1. 普通配置法

<struts>

<package name="struts2" extends="struts-default">

&

- IE中页面不居中,火狐谷歌等正常

aijuans

IE中页面不居中

问题是首页在火狐、谷歌、所有IE中正常显示,列表页的页面在火狐谷歌中正常,在IE6、7、8中都不中,觉得可能那个地方设置的让IE系列都不认识,仔细查看后发现,列表页中没写HTML模板部分没有添加DTD定义,就是<!DOCTYPE html PUBLIC "-//W3C//DTD XHTML 1.0 Transitional//EN" "http://www.w3

- String,int,Integer,char 几个类型常见转换

antonyup_2006

htmlsql.net

如何将字串 String 转换成整数 int?

int i = Integer.valueOf(my_str).intValue();

int i=Integer.parseInt(str);

如何将字串 String 转换成Integer ?

Integer integer=Integer.valueOf(str);

如何将整数 int 转换成字串 String ?

1.

- PL/SQL的游标类型

百合不是茶

显示游标(静态游标)隐式游标游标的更新和删除%rowtyperef游标(动态游标)

游标是oracle中的一个结果集,用于存放查询的结果;

PL/SQL中游标的声明;

1,声明游标

2,打开游标(默认是关闭的);

3,提取数据

4,关闭游标

注意的要点:游标必须声明在declare中,使用open打开游标,fetch取游标中的数据,close关闭游标

隐式游标:主要是对DML数据的操作隐

- JUnit4中@AfterClass @BeforeClass @after @before的区别对比

bijian1013

JUnit4单元测试

一.基础知识

JUnit4使用Java5中的注解(annotation),以下是JUnit4常用的几个annotation: @Before:初始化方法 对于每一个测试方法都要执行一次(注意与BeforeClass区别,后者是对于所有方法执行一次)@After:释放资源 对于每一个测试方法都要执行一次(注意与AfterClass区别,后者是对于所有方法执行一次

- 精通Oracle10编程SQL(12)开发包

bijian1013

oracle数据库plsql

/*

*开发包

*包用于逻辑组合相关的PL/SQL类型(例如TABLE类型和RECORD类型)、PL/SQL项(例如游标和游标变量)和PL/SQL子程序(例如过程和函数)

*/

--包用于逻辑组合相关的PL/SQL类型、项和子程序,它由包规范和包体两部分组成

--建立包规范:包规范实际是包与应用程序之间的接口,它用于定义包的公用组件,包括常量、变量、游标、过程和函数等

--在包规

- 【EhCache二】ehcache.xml配置详解

bit1129

ehcache.xml

在ehcache官网上找了多次,终于找到ehcache.xml配置元素和属性的含义说明文档了,这个文档包含在ehcache.xml的注释中!

ehcache.xml : http://ehcache.org/ehcache.xml

ehcache.xsd : http://ehcache.org/ehcache.xsd

ehcache配置文件的根元素是ehcahe

ehcac

- java.lang.ClassNotFoundException: org.springframework.web.context.ContextLoaderL

白糖_

javaeclipsespringtomcatWeb

今天学习spring+cxf的时候遇到一个问题:在web.xml中配置了spring的上下文监听器:

<listener>

<listener-class>org.springframework.web.context.ContextLoaderListener</listener-class>

</listener>

随后启动

- angular.element

boyitech

AngularJSAngularJS APIangular.element

angular.element

描述: 包裹着一部分DOM element或者是HTML字符串,把它作为一个jQuery元素来处理。(类似于jQuery的选择器啦) 如果jQuery被引入了,则angular.element就可以看作是jQuery选择器,选择的对象可以使用jQuery的函数;如果jQuery不可用,angular.e

- java-给定两个已排序序列,找出共同的元素。

bylijinnan

java

import java.util.ArrayList;

import java.util.Arrays;

import java.util.List;

public class CommonItemInTwoSortedArray {

/**

* 题目:给定两个已排序序列,找出共同的元素。

* 1.定义两个指针分别指向序列的开始。

* 如果指向的两个元素

- sftp 异常,有遇到的吗?求解

Chen.H

javajcraftauthjschjschexception

com.jcraft.jsch.JSchException: Auth cancel

at com.jcraft.jsch.Session.connect(Session.java:460)

at com.jcraft.jsch.Session.connect(Session.java:154)

at cn.vivame.util.ftp.SftpServerAccess.connec

- [生物智能与人工智能]神经元中的电化学结构代表什么?

comsci

人工智能

我这里做一个大胆的猜想,生物神经网络中的神经元中包含着一些化学和类似电路的结构,这些结构通常用来扮演类似我们在拓扑分析系统中的节点嵌入方程一样,使得我们的神经网络产生智能判断的能力,而这些嵌入到节点中的方程同时也扮演着"经验"的角色....

我们可以尝试一下...在某些神经

- 通过LAC和CID获取经纬度信息

dai_lm

laccid

方法1:

用浏览器打开http://www.minigps.net/cellsearch.html,然后输入lac和cid信息(mcc和mnc可以填0),如果数据正确就可以获得相应的经纬度

方法2:

发送HTTP请求到http://www.open-electronics.org/celltrack/cell.php?hex=0&lac=<lac>&cid=&

- JAVA的困难分析

datamachine

java

前段时间转了一篇SQL的文章(http://datamachine.iteye.com/blog/1971896),文章不复杂,但思想深刻,就顺便思考了一下java的不足,当砖头丢出来,希望引点和田玉。

-----------------------------------------------------------------------------------------

- 小学5年级英语单词背诵第二课

dcj3sjt126com

englishword

money 钱

paper 纸

speak 讲,说

tell 告诉

remember 记得,想起

knock 敲,击,打

question 问题

number 数字,号码

learn 学会,学习

street 街道

carry 搬运,携带

send 发送,邮寄,发射

must 必须

light 灯,光线,轻的

front

- linux下面没有tree命令

dcj3sjt126com

linux

centos p安装

yum -y install tree

mac os安装

brew install tree

首先来看tree的用法

tree 中文解释:tree

功能说明:以树状图列出目录的内容。

语 法:tree [-aACdDfFgilnNpqstux][-I <范本样式>][-P <范本样式

- Map迭代方式,Map迭代,Map循环

蕃薯耀

Map循环Map迭代Map迭代方式

Map迭代方式,Map迭代,Map循环

>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>

蕃薯耀 2015年

- Spring Cache注解+Redis

hanqunfeng

spring

Spring3.1 Cache注解

依赖jar包:

<!-- redis -->

<dependency>

<groupId>org.springframework.data</groupId>

<artifactId>spring-data-redis</artifactId>

- Guava中针对集合的 filter和过滤功能

jackyrong

filter

在guava库中,自带了过滤器(filter)的功能,可以用来对collection 进行过滤,先看例子:

@Test

public void whenFilterWithIterables_thenFiltered() {

List<String> names = Lists.newArrayList("John"

- 学习编程那点事

lampcy

编程androidPHPhtml5

一年前的夏天,我还在纠结要不要改行,要不要去学php?能学到真本事吗?改行能成功吗?太多的问题,我终于不顾一切,下定决心,辞去了工作,来到传说中的帝都。老师给的乘车方式还算有效,很顺利的就到了学校,赶巧了,正好学校搬到了新校区。先安顿了下来,过了个轻松的周末,第一次到帝都,逛逛吧!

接下来的周一,是我噩梦的开始,学习内容对我这个零基础的人来说,除了勉强完成老师布置的作业外,我已经没有时间和精力去

- 架构师之流处理---------bytebuffer的mark,limit和flip

nannan408

ByteBuffer

1.前言。

如题,limit其实就是可以读取的字节长度的意思,flip是清空的意思,mark是标记的意思 。

2.例子.

例子代码:

String str = "helloWorld";

ByteBuffer buff = ByteBuffer.wrap(str.getBytes());

Sy

- org.apache.el.parser.ParseException: Encountered " ":" ": "" at line 1, column 1

Everyday都不同

$转义el表达式

最近在做Highcharts的过程中,在写js时,出现了以下异常:

严重: Servlet.service() for servlet jsp threw exception

org.apache.el.parser.ParseException: Encountered " ":" ": "" at line 1,

- 用Java实现发送邮件到163

tntxia

java实现

/*

在java版经常看到有人问如何用javamail发送邮件?如何接收邮件?如何访问多个文件夹等。问题零散,而历史的回复早已经淹没在问题的海洋之中。

本人之前所做过一个java项目,其中包含有WebMail功能,当初为用java实现而对javamail摸索了一段时间,总算有点收获。看到论坛中的经常有此方面的问题,因此把我的一些经验帖出来,希望对大家有些帮助。

此篇仅介绍用

- 探索实体类存在的真正意义

java小叶檀

POJO

一. 实体类简述

实体类其实就是俗称的POJO,这种类一般不实现特殊框架下的接口,在程序中仅作为数据容器用来持久化存储数据用的

POJO(Plain Old Java Objects)简单的Java对象

它的一般格式就是

public class A{

private String id;

public Str