- 手把手教你实现pynq-z2条形码识别

雪天鱼

我是雪天鱼,一名FPGA爱好者,研究方向是FPGA架构探索和SOC设计。关注公众号【集成电路设计教程】,拉你进“IC设计交流群”。1.前言单单实现一个二维码识别就花了将近一个星期,这篇文章我就详细介绍这段时间走过的坑,代码附在文末,着急需要的小伙伴直接翻到最后即可2.linux配置要想实现本项目,首先解决以下三大要点,也着实浪费了很多时间2.1解决pynq联网pynq联网的教程网上可谓是不少,但是

- 【基于xilinx Zynq7000的PYNQ框架项目】03 Socket实现开发板和电脑的实时视频传输并存储图片

小黄能吃辣

嵌入式硬件单片机tcp/ipopencvubuntu课程设计音视频

03socket实现实时视频流传输并保存前言一、服务器端代码二、客户端代码三、运行总结前言主机摄像头获取实时视频流,需要传输到开发板上并实时保存更新,才能使用开发板上的人脸识别模型进行人脸检测。本篇文章通过socket实现主机与ZYNQ_MINI开发板之间的数据传输。一、服务器端代码承接本项目系列的上一篇文章【基于XilinxZynq7000的PYNQ框架项目】02PYNQ镜像制作,使用PYNQ提

- 【基于Xilinx ZYNQ7000的PYNQ框架项目】01人脸识别项目介绍与展示

小黄能吃辣

单片机嵌入式硬件ubuntu软件工程课程设计目标检测tcp/ip

01项目介绍与展示前言一、项目内容环境与工具项目文件二、运行项目1.登录开发板2.运行代码3.效果展示总结前言 本项目是一个嵌入式开发的人脸识别项目,为开发板自制PYNQ镜像,通过socket通信将笔记本摄像头画面实时传输至开发板,然后使用开发板上的人脸识别模型进行检测后,将识别画面传输回笔记本进行显示。项目整体设计框架图如下所示:系统处理流程图如下所示:一、项目内容环境与工具开发板ZYNQ_M

- 【基于Xilinx Zynq7000的PYNQ框架项目】02 PYNQ镜像制作

小黄能吃辣

单片机嵌入式硬件ubuntu课程设计经验分享软件工程python

02PYNQ镜像制作前言一、vivado硬件设计二、ubuntu镜像制作三、Win32DiskImage烧写镜像四、上板启动总结前言由于PYNQ官网中没有适配ZYNQ_MINI开发板的现成的PYNQ镜像,我们需要用vivado自己设计硬件部分,然后下载与板子无关的预构建文件PYNQrootfs,在ubuntu系统中制作适配ZYNQ_MINI开发板的PYNQ镜像。软件与系统的环境版本Windows1

- 【基于Xilinx ZYNQ7000的PYNQ框架项目】04开发板上运行人脸识别模型

小黄能吃辣

嵌入式硬件opencv计算机视觉目标检测目标跟踪视觉检测图像处理

04开发板上运行人脸识别模型前言一、人脸识别代码详解总结前言书接上文,成功将电脑摄像头视频流传输到开发板并本地存储后,要做的就是使用PYNQ的pyhotn代码逐帧读取视频流,进行人脸识别啦。因为当初做这个项目的主要目的是锻炼嵌入式开发的能力,所以人脸识别模型是直接使用的opencv自带的分类器。(其实是懒得自己再捣鼓个模型了)我使用的分类器是haarcascade_frontalface_alt2

- 【基于Xilinx ZYNQ7000的PYNQ框架项目】05使用Overlay库和python父子进程实现开发板按键控制LED灯流水或熄灭

小黄能吃辣

python单片机嵌入式硬件fpga开发硬件工程opencv视觉检测

05使用Overlay库和python父子进程实现开发板按键控制LED灯流水或熄灭前言一、PYNQOverlay库的GPIO读写实现LED灯流水二、python父子进程实现按键即关闭程序总结前言前四篇文章完成后,其实整个项目就能完整运行起来了。但我们似乎忘了使用PYNQ的初心——用python编程实现对开发板硬件部分的控制。因此,本文章使用PYNQOverlay库的GPIO读写实现LED灯流水,然

- pynq?启动! pynq开发板连接宿主机+初始配置

物质波波波

计算机体系结构机器学习fpga开发

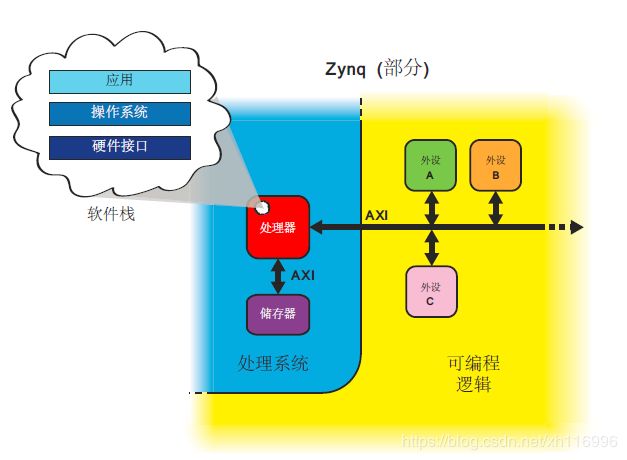

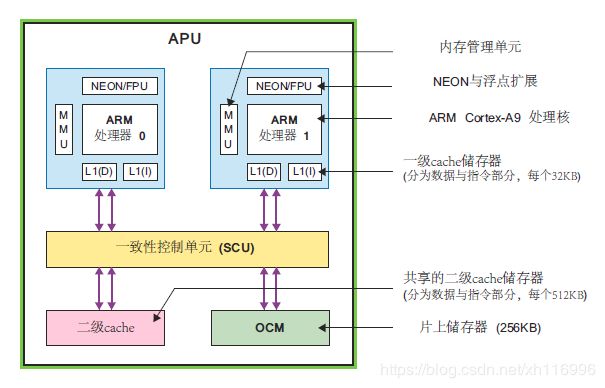

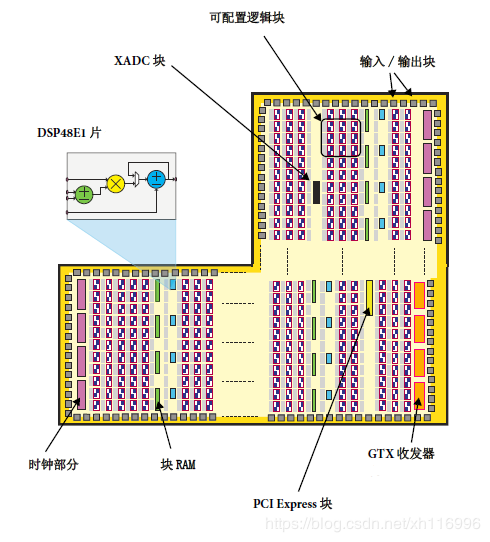

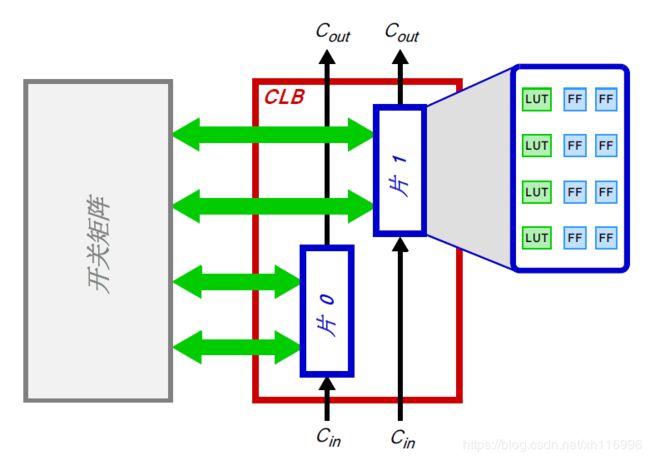

前言:pynq架构介绍“用FPGA写了个外挂,被暴雪认定是非法第三方程序用的PYNQ+STM32,PYNQ负责从HDMI截图并用OpenCV算法找到目标,并把坐标发给STM32。STM32实现USBHID鼠标,负责把准心移动到目标上。”PYNQ是一款可以用python玩的FPGA,其设计初衷是通过高层次的封装,将底层硬件FPGA实现细节与上层应用层的使用脱耦,对软件开发者来说,PYNQ框架已经提供

- 4—基于FPGA(ZYNQ-Z2)的多功能小车—软件设计—电机驱动模块

贡橙小白鼠

fpga开发

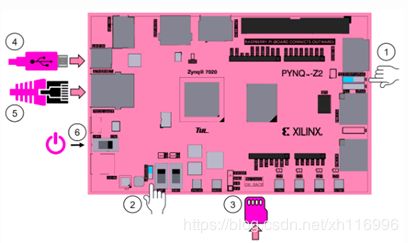

我使用的FPGA是Xilinx的PYNQ-7020(ZYNQ-Z2),在Vivado2018.3平台使用Verilog进行编程。目录1.电机驱动介绍:2.模块编写介绍:2.1Verilog代码2.2方向逻辑分析2.4PWM_Divider模块3.调用方法1.电机驱动介绍:使用TB6612FNG电机驱动,驱动一个电机需要FPGA对芯片有3个输入:IN1控制正反转IN2控制正反转PWM控制转速IN1I

- fpga python_PYNQ:使用Python进行FPGA开发

weixin_39657575

fpgapython

未经私信同意禁止转载!前言PYNQ就是python+ZYNQ的意思,简单来说就是使用python在Xilinx的ZYNQ平台上进行开发。是Xilinx开发的一个新的开源框架,使嵌入式编程人员能够在无需设计可编程逻辑电路的情况下即可充分发挥XilinxZynqAllProgrammableSoC(APSoC)的功能。PYNQ-Z2开发板是最近刚推出的低成本的支持PYQN开发环境的demo板。淘宝上单

- 基于PYNQ的RT-Thread移植

happydesigner

操作系统c语言arm开发ubuntuarm

配置需求操作系统:Windows10硬件设备:PYNQ-Z1开发环境:Vivado2018.3RT-Thread系统版本:https://gitee.com/rtthread/rt-thread,标签:V4.0.3移植步骤安装PYNQ-Z1的boardfile文件通过网址https://github.com/cathalmccabe/pynq-z1_board_files将下载好的PYNQ-Z1.

- Zynq 使用PYNQ AXIS DMA LoopBack实验

Simpreative

https://pynq.readthedocs.io/en/latest/pynq_libraries/dma.html#pynq-libraries-dmaIPconnectedtotheAXIMaster(HPorACPports)hasaccesstoPSDRAM.搭建Vivado工程,DMA环回,注意axi_dma只能叫这个名字(不一定)生成bit文件ExportBitstreamFil

- 视觉注意力收集

Scabbards_

1500深度学习笔记深度学习人工智能

参考博文:神经网络学习小记录64——Pytorch图像处理中注意力机制的解析与代码详解_pynq注意力机制_Bubbliiiing的博客-CSDN博客【计算机视觉】详解自注意力:Non-local模块与Self-attention(视觉注意力机制(一))_自注意力模块_何处闻韶的博客-CSDN博客参考视频:SEnet模块实现_哔哩哔哩_bilibili视觉注意力代码汇总仓库:GitHub-Meng

- 复现基于PYNQ-Z2的手写数字识别卷积加速器设计

eachanm

FPGAverilogfpga

来源雪天鱼基于PYNQ-Z2的手写数字识别卷积加速器设计【持续更新】_雪天鱼的博客-CSDN博客一、设计思路1、输入28x28的图片,非png格式,而是txt格式,将图片数据进行量化,存入到txt文件当中。2、在PL端实现卷积神经网络LeNet-5,纯verilog实现,包括卷积层,激活层,池化层,全连接层。3、在PS端输出识别的结果。LeNet-5神经网络卷积:28X28的图片,我们采用6个5X

- pynq z2约束文件

人工智能和FPGA AI技术

fpga开发

set_propertyPACKAGE_PINset_propertyPACKAGE_PINAF25[get_portsrst]将信号名rst绑定AF25引脚,其他信号同理set_propertyIOSTANDARDLVCMOS33set_propertyIOSTANDARDLVCMOS33[get_portsrst]将信号名rst电平定义为LVCMOS33,就是3.3v电平set_propert

- pynq-1 viaodo配置和启动uboot

kissskill

pynq-1zynqlinuxuboot

Pynq-Z1u-boot移植笔记Author:(2022.10.21)创建vivado,生成bistream,因为前期不清楚芯片pynq-z1如何配置时钟和ddr部分,可以网上下载boardfile,然后在vivado安装目录下,新建board_file目录,将pynq-z1boardfile放在此目录,就可以在vivado的board部分看到pynq-z1板卡,直接选中,然后新建clock,d

- 怎么使用 pynq-z2 启动果壳

shimly123456

fpga开发

非常感谢郑州大学和计算所联培刘澳编写的资料:https://www.cnblogs.com/GrootStudy/p/17059382.htmlCompilechiselcode这里是英文版,之后会编写一个中文beforestart,gitcheckoutrelease-21228Installmill.RefertotheManualsectioninthisguide.Runmakeveril

- vivado 添加 pynq-z2板

頔枫

FPGAfpga开发

以vivado2019.02版本为例1下载地址https://www.tulembedded.com/FPGA/ProductsPYNQ-Z2.html2.点击下载3.解压添加注:如果没有board_files可以自己创建一个4.重新打开vivado

- PicoRV32-on-PYNQ-Z2: An FPGA-based SoC System——RISC-V On PYNQ项目复现

Mundane-_-

PicoRV32-on-PYNQ-Z2:AnFPGA-basedSoCSystem——RISC-VOnPYNQ项目复现

- PYNQ-Z2安装keras库的方法

爱阳阳963

PYNQ-Z2是基于armv7l平台,使用pip3直接安装keras时会报错,如下:Infileincludedfrom/tmp/pip-build-taykg8ym/h5py/h5py/defs.c:528:0:/tmp/pip-build-taykg8ym/h5py/h5py/api_compat.h:27:10:fatalerror:hdf5.h:Nosuchfileordirectory#

- 基于PYNQ实现神经网络目标识别——总贴

气气,

pynq实现目标识别神经网络网络人工智能

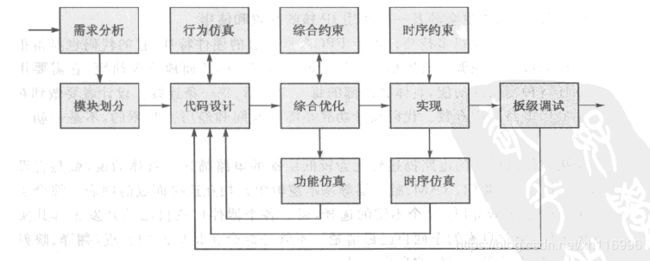

项目干了一半了,一共有3项:有监督(完结)小样本(识别速度需要优化)无监督(10.30开始)打算做无监督这一项的同时开始记录这一整套的流程:1.python生成较好的网络模型。2.将网络模型中所有权重及偏差参数导出生成为.bin文件。3.在vivadohls中以C语言复现网络模型,获取权重.bin文件参数固化在网络代码中,并导入testbench文件验证C语言复现神经网络的正误。4.在vivado

- 如何在PYNQ和ZYNQ上用FPGA加速神经网络

QQ3036003892

转载https://blog.csdn.net/qq_35999634/article/details/81672331如何在PYNQ和ZYNQ上用FPGA加速神经网络在PYNQ上顶层用Python调用,但是准备工作是框架(如:tensorflow)和IP(如:CNN),IP部分要自己在VivadoHLS(基于OpenCL)里面用C/C++或图形化界面进行设计,最后生成一个.bit和一个.tcl文

- 基于PYNQ-Z2的手写数字识别卷积加速器设计【持续更新】

雪天鱼

深度学习深度学习CNN硬件加速器设计

我是雪天鱼,一名FPGA爱好者,研究方向是FPGA架构探索和数字IC设计。关注公众号【集成电路设计教程】,获取更多学习资料,并拉你进“IC设计交流群”。QQIC设计&FPGA&DL交流群群号:866169462。项目开源地址:https://gitee.com/jccao/cnn_accelerator/tree/master/目前暂时以视频形式分享设计思路与过程。(1)滑窗模块设计与仿真(2)硬

- 【Takk系列】Zynq\FPGA\PYNQ实现的CNN LeNet加速系列视频教学

Taneeyo

TAKK系列fpga开发cnn人工智能zynq

该系列由浅入深,核心代码行行编写并实时讲解,由7个部分组成:神经网络的理论基础:包括神经元结构,感知机模型,反向传播等理论介绍以及Matlab实现。便于各位对后续CNN模型有一个理论基础。卷积神经网络CNN理论基础:包括卷积运算、池化、激活函数、全连接网络层等介绍,同时使用Matlab实现,手写网络,不调用第三方集成库,让各位能够清晰明了实际运算的过程。这是后续进行并行优化设计的基础。CNN硬件优

- 基于pynq的数字识别神经网络加速器设计

Jacob.Ge

神经网络tensorflowpythonfpga开发

文章目录基于pynq的数字识别神经网络加速器设计软件部分1.全连接神经网络:2.卷积神经网络搭建:3.文件格式转换:硬件部分1.MNIST的硬件实现思路2.代码编写与硬件综合3.硬件平台的搭建软硬件协同部分1.硬件驱动的编写:2.功能代码编写:基于pynq的数字识别神经网络加速器设计本篇为笔者第一次进行神经网络加速器设计的工程开发流程,在此做如下整理。python环境:python:3.6.13;

- 机器学习基础以及在pynq-Z2上部署Faster-RCNN的项目学习1

qq_51441754

fpga开发神经网络

目录一.python代码基础1.1.原始数据类型与操作1.1.1.数值型1.1.2.布尔型1.1.3.字符串1.1.4.其他1.2.变量与集合1.2.1.输入输出1.2.2.列表(List)1.2.3.元组(Tuple)1.2.4.字典(Dictionaries)1.2.5.集合(Set)1.3.控制流1.3.1.分支结构1.3.2.循环结构1.3.3.异常处理1.3.4.迭代器1.3.5.函数1

- pycharm中库安装+opencv手势识别

末欢

python_opencvpythonopencv

pycharm中库安装+opencv手势识别python开发编译环境搭建百度API申请流程python开发编译环境搭建近期需要使用PYNQ开发板做一手势识别的项目,在此做一些学习笔记,供随时翻阅及他人参考。安装pycharmpython及opencv安装可参考:链接:link.国内常用的源及cmd命令行下如何换源:链接:link.pycharm中如何换源及库的安装进入设置的该路径下,点击“+”,其

- 探索 Zynq MPSoC:配套 PYNQ 和机器学习应用一起使用 - 序言鸣谢目录20211231

芯选

探索Zynq®MPSoC机器学习fpga开发人工智能ZynqMPSoC

写在前面的话:看到朋友圈分享的这本书,一时技痒,给自己定个小目标,从今天开始翻译本书,作为小白学习FPGA之路的记录,仅供个人学习之用,并非用于任何商业目的。仅发布于知乎、个人CSDN博客和/或个人微信公众号。这是我的个人译文,鉴于个人能力有限,难免有疏漏之处。不代表任何官方对于所提及的任何技术的陈述。全书20余万字,2022年-2023年希望能够有始有终完成。——译者注,2021年12月28日探

- zynq设计学习笔记5——AXI_GPIO之按键中断控制LED灯实验

墨漓_lyl

FPGA之zynq设计学习笔记fpga嵌入式arm

在本实验中,我们将通过调用AXIGPIOIP核,使用中断机制,实现底板上PL端按键控制PS端GPIO,并使用EMIO控制LED灯的亮灭。首先,axi_gpio与之前的GPIO的区别:之前的GPIO是硬核,是ps端实际存在的外设电路;而axi_gpio是软核,实现的时候需要由fpga的pl端去搭建。下面为实验步骤:第一步:根据建立Vivado工程,本设计所使用的开发板为pynq-z2。再Create

- Zedboard编译PYNQ v2.6 并定制kernel 添加WiFi

Simpreative

0.安装PYNQ前先安装好Vivado,Petalinux2020.11.将PYNQ2.6.1下载到本地Documentshttps://github.com/Xilinx/PYNQ/releases/tag/v2.6.1或者gitclonehttps://github.com/Xilinx/PYNQgitstatusgitcheckoutimage_v2.7gitfetchgitrebaseor

- PYNQ2.6.0 petalinux2020.1 vivado2020.1 for zcu102

Leo_whj

PYNQfpga开发

PYNQ2.6.0petalinux2020.1vivado2020.1vitis2020.1forzcu102failed1、设置相关环境gitclonehttps://github.com/Xilinx/PYNQ.gitcdPYNQgitcheckoutv2.6.0gitcheckout-bZCU102source./sdbuild/scripts/setup_host.sh设置环境:sour

- jQuery 跨域访问的三种方式 No 'Access-Control-Allow-Origin' header is present on the reque

qiaolevip

每天进步一点点学习永无止境跨域众观千象

XMLHttpRequest cannot load http://v.xxx.com. No 'Access-Control-Allow-Origin' header is present on the requested resource. Origin 'http://localhost:63342' is therefore not allowed access. test.html:1

- mysql 分区查询优化

annan211

java分区优化mysql

分区查询优化

引入分区可以给查询带来一定的优势,但同时也会引入一些bug.

分区最大的优点就是优化器可以根据分区函数来过滤掉一些分区,通过分区过滤可以让查询扫描更少的数据。

所以,对于访问分区表来说,很重要的一点是要在where 条件中带入分区,让优化器过滤掉无需访问的分区。

可以通过查看explain执行计划,是否携带 partitions

- MYSQL存储过程中使用游标

chicony

Mysql存储过程

DELIMITER $$

DROP PROCEDURE IF EXISTS getUserInfo $$

CREATE PROCEDURE getUserInfo(in date_day datetime)-- -- 实例-- 存储过程名为:getUserInfo-- 参数为:date_day日期格式:2008-03-08-- BEGINdecla

- mysql 和 sqlite 区别

Array_06

sqlite

转载:

http://www.cnblogs.com/ygm900/p/3460663.html

mysql 和 sqlite 区别

SQLITE是单机数据库。功能简约,小型化,追求最大磁盘效率

MYSQL是完善的服务器数据库。功能全面,综合化,追求最大并发效率

MYSQL、Sybase、Oracle等这些都是试用于服务器数据量大功能多需要安装,例如网站访问量比较大的。而sq

- pinyin4j使用

oloz

pinyin4j

首先需要pinyin4j的jar包支持;jar包已上传至附件内

方法一:把汉字转换为拼音;例如:编程转换后则为biancheng

/**

* 将汉字转换为全拼

* @param src 你的需要转换的汉字

* @param isUPPERCASE 是否转换为大写的拼音; true:转换为大写;fal

- 微博发送私信

随意而生

微博

在前面文章中说了如和获取登陆时候所需要的cookie,现在只要拿到最后登陆所需要的cookie,然后抓包分析一下微博私信发送界面

http://weibo.com/message/history?uid=****&name=****

可以发现其发送提交的Post请求和其中的数据,

让后用程序模拟发送POST请求中的数据,带着cookie发送到私信的接入口,就可以实现发私信的功能了。

- jsp

香水浓

jsp

JSP初始化

容器载入JSP文件后,它会在为请求提供任何服务前调用jspInit()方法。如果您需要执行自定义的JSP初始化任务,复写jspInit()方法就行了

JSP执行

这一阶段描述了JSP生命周期中一切与请求相关的交互行为,直到被销毁。

当JSP网页完成初始化后

- 在 Windows 上安装 SVN Subversion 服务端

AdyZhang

SVN

在 Windows 上安装 SVN Subversion 服务端2009-09-16高宏伟哈尔滨市道里区通达街291号

最佳阅读效果请访问原地址:http://blog.donews.com/dukejoe/archive/2009/09/16/1560917.aspx

现在的Subversion已经足够稳定,而且已经进入了它的黄金时段。我们看到大量的项目都在使

- android开发中如何使用 alertDialog从listView中删除数据?

aijuans

android

我现在使用listView展示了很多的配置信息,我现在想在点击其中一条的时候填出 alertDialog,点击确认后就删除该条数据,( ArrayAdapter ,ArrayList,listView 全部删除),我知道在 下面的onItemLongClick 方法中 参数 arg2 是选中的序号,但是我不知道如何继续处理下去 1 2 3

- jdk-6u26-linux-x64.bin 安装

baalwolf

linux

1.上传安装文件(jdk-6u26-linux-x64.bin)

2.修改权限

[root@localhost ~]# ls -l /usr/local/jdk-6u26-linux-x64.bin

3.执行安装文件

[root@localhost ~]# cd /usr/local

[root@localhost local]# ./jdk-6u26-linux-x64.bin&nbs

- MongoDB经典面试题集锦

BigBird2012

mongodb

1.什么是NoSQL数据库?NoSQL和RDBMS有什么区别?在哪些情况下使用和不使用NoSQL数据库?

NoSQL是非关系型数据库,NoSQL = Not Only SQL。

关系型数据库采用的结构化的数据,NoSQL采用的是键值对的方式存储数据。

在处理非结构化/半结构化的大数据时;在水平方向上进行扩展时;随时应对动态增加的数据项时可以优先考虑使用NoSQL数据库。

在考虑数据库的成熟

- JavaScript异步编程Promise模式的6个特性

bijian1013

JavaScriptPromise

Promise是一个非常有价值的构造器,能够帮助你避免使用镶套匿名方法,而使用更具有可读性的方式组装异步代码。这里我们将介绍6个最简单的特性。

在我们开始正式介绍之前,我们想看看Javascript Promise的样子:

var p = new Promise(function(r

- [Zookeeper学习笔记之八]Zookeeper源代码分析之Zookeeper.ZKWatchManager

bit1129

zookeeper

ClientWatchManager接口

//接口的唯一方法materialize用于确定那些Watcher需要被通知

//确定Watcher需要三方面的因素1.事件状态 2.事件类型 3.znode的path

public interface ClientWatchManager {

/**

* Return a set of watchers that should

- 【Scala十五】Scala核心九:隐式转换之二

bit1129

scala

隐式转换存在的必要性,

在Java Swing中,按钮点击事件的处理,转换为Scala的的写法如下:

val button = new JButton

button.addActionListener(

new ActionListener {

def actionPerformed(event: ActionEvent) {

- Android JSON数据的解析与封装小Demo

ronin47

转自:http://www.open-open.com/lib/view/open1420529336406.html

package com.example.jsondemo;

import org.json.JSONArray;

import org.json.JSONException;

import org.json.JSONObject;

impor

- [设计]字体创意设计方法谈

brotherlamp

UIui自学ui视频ui教程ui资料

从古至今,文字在我们的生活中是必不可少的事物,我们不能想象没有文字的世界将会是怎样。在平面设计中,UI设计师在文字上所花的心思和功夫最多,因为文字能直观地表达UI设计师所的意念。在文字上的创造设计,直接反映出平面作品的主题。

如设计一幅戴尔笔记本电脑的广告海报,假设海报上没有出现“戴尔”两个文字,即使放上所有戴尔笔记本电脑的图片都不能让人们得知这些电脑是什么品牌。只要写上“戴尔笔

- 单调队列-用一个长度为k的窗在整数数列上移动,求窗里面所包含的数的最大值

bylijinnan

java算法面试题

import java.util.LinkedList;

/*

单调队列 滑动窗口

单调队列是这样的一个队列:队列里面的元素是有序的,是递增或者递减

题目:给定一个长度为N的整数数列a(i),i=0,1,...,N-1和窗长度k.

要求:f(i) = max{a(i-k+1),a(i-k+2),..., a(i)},i = 0,1,...,N-1

问题的另一种描述就

- struts2处理一个form多个submit

chiangfai

struts2

web应用中,为完成不同工作,一个jsp的form标签可能有多个submit。如下代码:

<s:form action="submit" method="post" namespace="/my">

<s:textfield name="msg" label="叙述:">

- shell查找上个月,陷阱及野路子

chenchao051

shell

date -d "-1 month" +%F

以上这段代码,假如在2012/10/31执行,结果并不会出现你预计的9月份,而是会出现八月份,原因是10月份有31天,9月份30天,所以-1 month在10月份看来要减去31天,所以直接到了8月31日这天,这不靠谱。

野路子解决:假设当天日期大于15号

- mysql导出数据中文乱码问题

daizj

mysql中文乱码导数据

解决mysql导入导出数据乱码问题方法:

1、进入mysql,通过如下命令查看数据库编码方式:

mysql> show variables like 'character_set_%';

+--------------------------+----------------------------------------+

| Variable_name&nbs

- SAE部署Smarty出现:Uncaught exception 'SmartyException' with message 'unable to write

dcj3sjt126com

PHPsmartysae

对于SAE出现的问题:Uncaught exception 'SmartyException' with message 'unable to write file...。

官方给出了详细的FAQ:http://sae.sina.com.cn/?m=faqs&catId=11#show_213

解决方案为:

01

$path

- 《教父》系列台词

dcj3sjt126com

Your love is also your weak point.

你的所爱同时也是你的弱点。

If anything in this life is certain, if history has taught us anything, it is

that you can kill anyone.

不顾家的人永远不可能成为一个真正的男人。 &

- mongodb安装与使用

dyy_gusi

mongo

一.MongoDB安装和启动,widndows和linux基本相同

1.下载数据库,

linux:mongodb-linux-x86_64-ubuntu1404-3.0.3.tgz

2.解压文件,并且放置到合适的位置

tar -vxf mongodb-linux-x86_64-ubun

- Git排除目录

geeksun

git

在Git的版本控制中,可能有些文件是不需要加入控制的,那我们在提交代码时就需要忽略这些文件,下面讲讲应该怎么给Git配置一些忽略规则。

有三种方法可以忽略掉这些文件,这三种方法都能达到目的,只不过适用情景不一样。

1. 针对单一工程排除文件

这种方式会让这个工程的所有修改者在克隆代码的同时,也能克隆到过滤规则,而不用自己再写一份,这就能保证所有修改者应用的都是同一

- Ubuntu 创建开机自启动脚本的方法

hongtoushizi

ubuntu

转载自: http://rongjih.blog.163.com/blog/static/33574461201111504843245/

Ubuntu 创建开机自启动脚本的步骤如下:

1) 将你的启动脚本复制到 /etc/init.d目录下 以下假设你的脚本文件名为 test。

2) 设置脚本文件的权限 $ sudo chmod 755

- 第八章 流量复制/AB测试/协程

jinnianshilongnian

nginxluacoroutine

流量复制

在实际开发中经常涉及到项目的升级,而该升级不能简单的上线就完事了,需要验证该升级是否兼容老的上线,因此可能需要并行运行两个项目一段时间进行数据比对和校验,待没问题后再进行上线。这其实就需要进行流量复制,把流量复制到其他服务器上,一种方式是使用如tcpcopy引流;另外我们还可以使用nginx的HttpLuaModule模块中的ngx.location.capture_multi进行并发

- 电商系统商品表设计

lkl

DROP TABLE IF EXISTS `category`; -- 类目表

/*!40101 SET @saved_cs_client = @@character_set_client */;

/*!40101 SET character_set_client = utf8 */;

CREATE TABLE `category` (

`id` int(11) NOT NUL

- 修改phpMyAdmin导入SQL文件的大小限制

pda158

sqlmysql

用phpMyAdmin导入mysql数据库时,我的10M的

数据库不能导入,提示mysql数据库最大只能导入2M。

phpMyAdmin数据库导入出错: You probably tried to upload too large file. Please refer to documentation for ways to workaround this limit.

- Tomcat性能调优方案

Sobfist

apachejvmtomcat应用服务器

一、操作系统调优

对于操作系统优化来说,是尽可能的增大可使用的内存容量、提高CPU的频率,保证文件系统的读写速率等。经过压力测试验证,在并发连接很多的情况下,CPU的处理能力越强,系统运行速度越快。。

【适用场景】 任何项目。

二、Java虚拟机调优

应该选择SUN的JVM,在满足项目需要的前提下,尽量选用版本较高的JVM,一般来说高版本产品在速度和效率上比低版本会有改进。

J

- SQLServer学习笔记

vipbooks

数据结构xml

1、create database school 创建数据库school

2、drop database school 删除数据库school

3、use school 连接到school数据库,使其成为当前数据库

4、create table class(classID int primary key identity not null)

创建一个名为class的表,其有一