Vivado初学笔记

一、Xilinx 芯片类型(转自赛灵思官网)

目前学习的是7系列。性能从低到高:SPARTAN,ARTIX,LINTEX,VIRTEX。

芯片的内部资源在官网中也有介绍,此处就不贴了。

二、Vivado安装

由于电脑系统是win7的,所以在安装Vivado18.1时安装失败,只能安装16.4。看来以后的电脑系统要转用win10了。

三、Modelsim安装

安装Modelsim时,破解时注意创建系统环境变量时的路径,如C:\modeltech_10.5\LICENSE.TXT。注意要有LICENSE.TXT。(唉,一言难尽)需要再重启电脑

四、点亮LED(转自黑金用户手册)

在刚接触Vivado时,以黑金AX7103开发板的用户指导手册作为参考。(全名《黑金AX7103开发板Verilog教程V1.0pdf》)

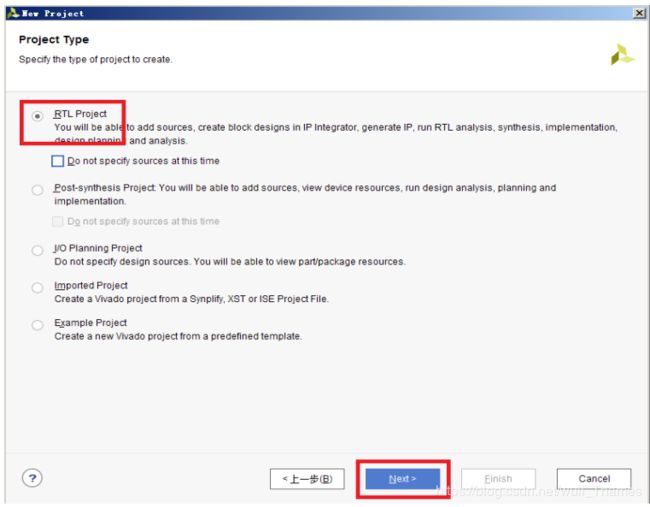

创建工程

IBUFGDS原语 (FPGA中还有其他的原语)

因为开发板中输入的是差分时钟,而程序中用的是单端时钟,所以需要调用一个IBUFGDS的原语将差分全局时钟转换成单端全局时钟。(IBUFGDS是IBUFG的差分形式,当信号从一对差分全局时钟管脚输入时,必须使用IBUFGDS作为全局时钟输入缓冲)

IBUFGDS #

(

.DIFF_TERM ("FALSE"),

.IBUF_LOW_PWR("FALSE")

)

u_ibufg_sys_clk

(

.I(sys_clk_p), //此处连接差分时钟信号 正极

.IB(sys_clk_n), //此处连接差分时钟信号 负极

.O(sclk) //此处连接程序中要使用的 单端时钟

);添加引脚约束文件(XDC)

XDC文件主要完成管脚的约束、时钟的约束、组的约束。

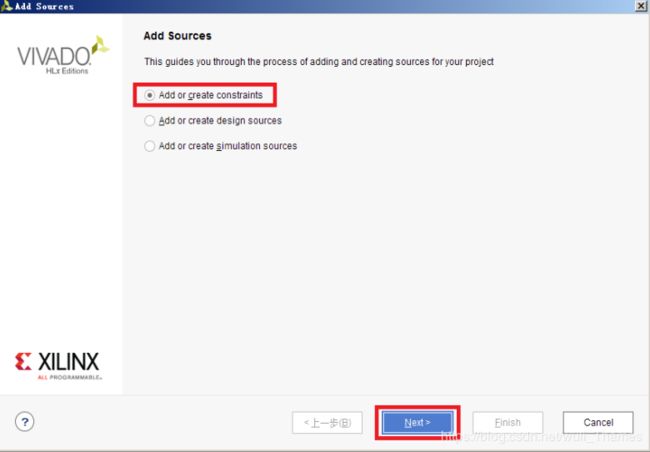

添加程序文件时是Add Sources >> Add or create design sources

添加引脚约束文件是Add Sources >>Add or create constraints

引脚定义文件中的内容,以该例程点亮LED为例:

set_property CFGBVS VCCIO [current_design]

set_property CONFIG_VOLTAGE 3.3 [current_design]

############## clock define##################

create_clock -period 5 [get_ports sys_clk_p] //差分时钟的时钟周期为5ns

set_property PACKAGE_PIN R4 [get_ports sys_clk_p]

set_property IOSTANDARD DIFF_SSTL15 [get_ports sys_clk_p]

############## key define##################

set_property PACKAGE_PIN T6 [get_ports rst_n]

set_property IOSTANDARD LVCMOS15 [get_ports rst_n] //电压为1.5V

##############LED define##################

set_property PACKAGE_PIN C17 [get_ports {led[0]}] //数组时要用{ }

set_property IOSTANDARD LVCMOS33 [get_ports {led[0]}] //电压为3.3V

set_property PACKAGE_PIN D17 [get_ports {led[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[1]}]

set_property PACKAGE_PIN V20 [get_ports {led[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[2]}]

set_property PACKAGE_PIN U20 [get_ports {led[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[3]}]

#############SPI Configurate Setting################## //提高SPI FLASH的读写时钟

set_property BITSTREAM.CONFIG.SPI_BUSWIDTH 4 [current_design]

set_property CONFIG_MODE SPIx4 [current_design] //使用X4的方式读写

set_property BITSTREAM.CONFIG.CONFIGRATE 50 [current_design](1)前面两句是配置CFGBVS引脚的电压和配置电路的电压。

在黑金开发板上CFGBVS引脚(即BANK 0 的VCCIO)是上拉到3.3V;配置电路的电压也是3.3V。

(2)基本XDC编写语法(按对编写)

(2.1) set_property PACKAGE_PIN "引脚编号" [get_ports “端口名称” ]

电平信号癿约束如下:

(2.2) set_property IOSTANDARD "电压" [get_ports “端口名称” ]

需要注意文字的大小写;端口名称是数组的话需要用{ }括起来(led信号)。端口名必须和源代码中的名字一致。

(2.3)create_clock -period "周期" [get_ports “端口名称” ]

时钟引脚还需要定义时钟周期约束,差分时钟只需要定义和约束 P 引脚。此处的周期单位为ns。

(3)防止固化后,关电后重新上电需要等好长时间。所以对SPI FLASH也进行了时钟约束。

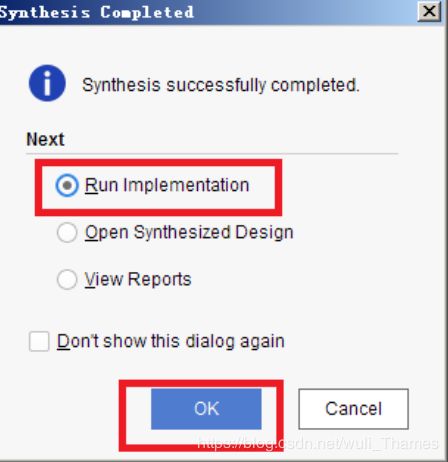

编译

(1)点击 Run Synthesis,即可开始综合并生成网表文件

(2)点击 Run Implementation,开始布局布线

(3)点击Generate Bitstream,生成 bit 文件

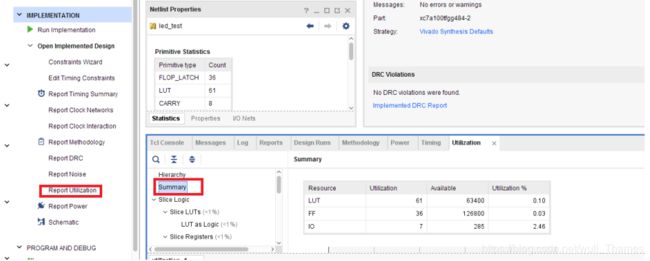

(4)点击 Implementation >> Report Utilization 查看板子实际资源使用情况:LUT(查找表)、FF(寄存器)、IO(管脚)、BUFG(时钟Buffer)

仿真

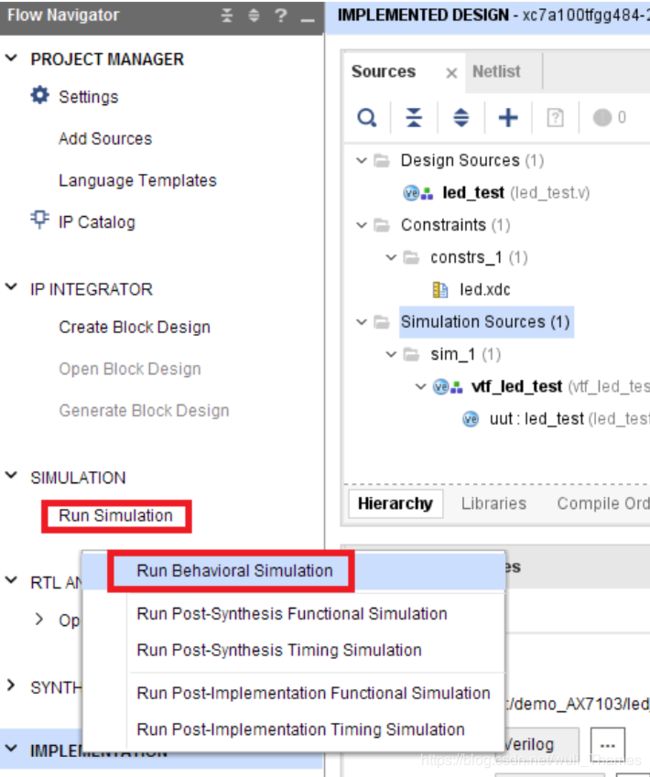

(1)设置vivado仿真配置,点击 Simulation >> Simulation Setting,将Simulation栏中的xsim.simulate.runtime 根据需要修改,其他按默认设置即可。

(2)添加测试文件。Add Sources >> Add or create simulation sources。

(3)编写测试文件

`timescale 100ps / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Module Name: vtf_led_test

//////////////////////////////////////////////////////////////////////////////////

module vtf_led_test;

// Inputs

reg sys_clk_p;

wire sys_clk_n;

reg rst_n;

// Outputs

wire [3:0] led;

// Instantiate the Unit Under Test (UUT)

led_test uut (

.sys_clk_p(sys_clk_p),

.sys_clk_n(sys_clk_n),

.rst_n(rst_n),

.led(led)

);

initial begin

// Initialize Inputs

sys_clk_p = 0;

rst_n = 0;

// Wait 100 ns for global reset to finish

#1000;

rst_n = 1;

// Add stimulus here, stop simulation after 2ms

#20000;

$stop;

end

always #25 sys_clk_p = ~ sys_clk_p; //5ns 一个周期,产生 200MHz 时钟源,timescale是100ns

assign sys_clk_n=~sys_clk_p; //此处需要注意

endmodule(4)点击 Run Simulation >> Run Behavioral Simulation

下载和调试

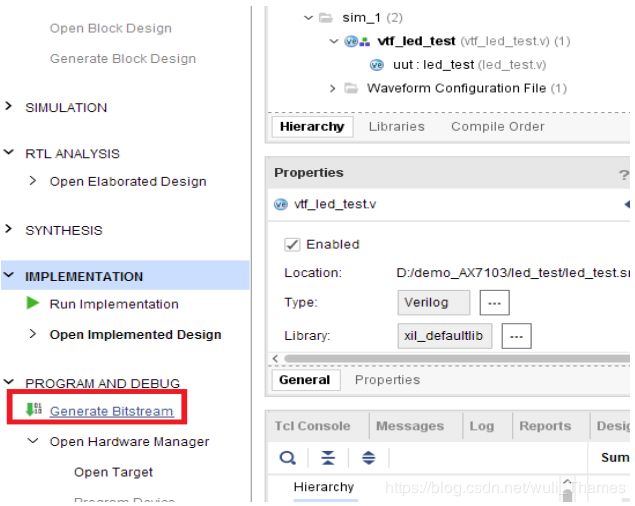

(1)右键Program And Debug >> Bitstream Setting...;-bit_file打勾,其他不打勾。

(2)点击Generate Bitstream 产生 bit 文件和 bin 文件。

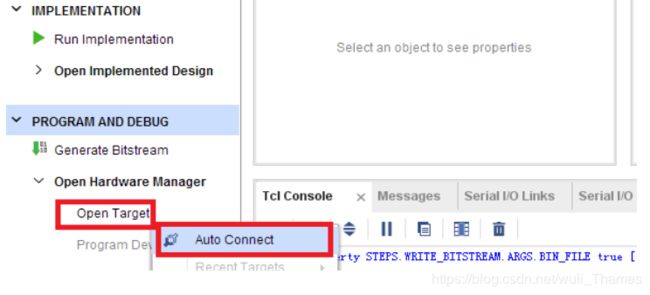

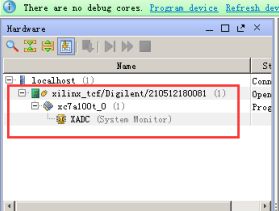

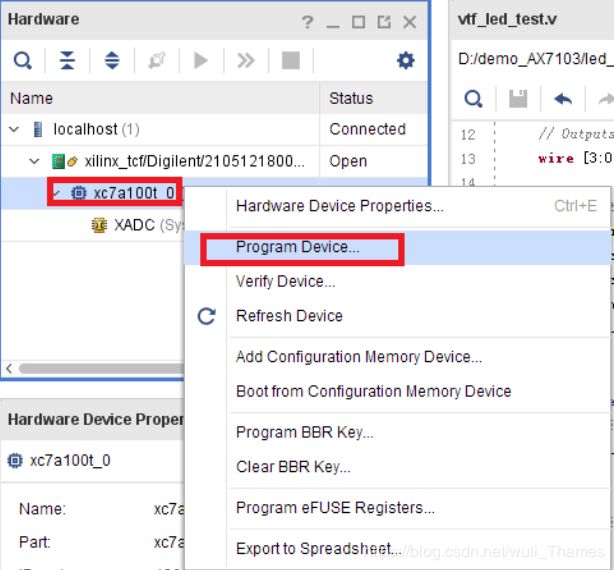

(3)点击Program And Debug >> Open Hardware Manager >> Open Target >> Auto Connect ,在Hardware界面下显示xc71100t_0 的图表说明JTAG已经建立连接。

(4)右键xc71100t_0 >> Program Device

(5)软件会自动选择项目生成的 bit 件,点击Program即可。

固化

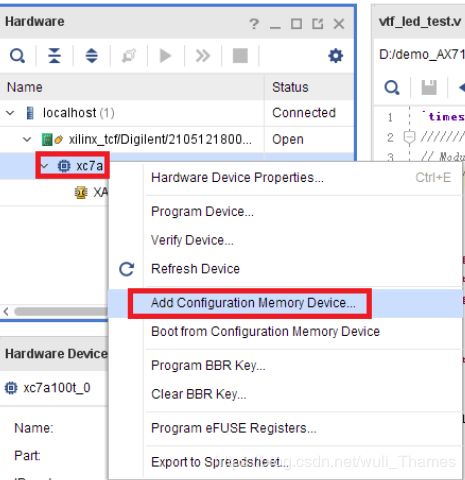

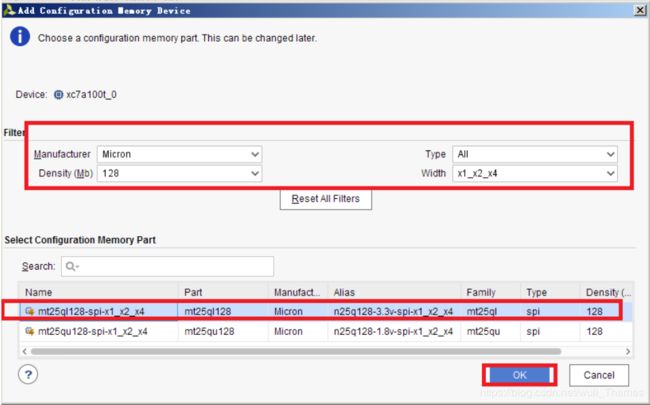

(1)右键xc71100t_0 >> Add Configuration Memory Device...

(2)选择FLASH型号

(3)在弹出的 Program Configuration Memory Device 窗口中,Configration file 选择生成的 .bin 文件。

(4)点击OK,开始编程FLASH