- [Verilog]模块实例化驱动的理解

Jason_Tye

fpga开发

笔者在复习刷题HDLBits时,对模块实例化时,接口的驱动有了更深理解.问题描述实现100位的带涟漪进位(ripple-carry)的全加器处理过程这是一个纯组合逻辑电路,除了可能在CombinationalBlocksalways@(*)中进行的赋值外,无需reg,所以默认的wire类型不予显式.首先实现单位全加器full_addermodulefadd(inputa;inputb;inputc

- HDLBits刷题Day23,3.2.5.7 Simple FSM 3 (asynchronous reset) - 3.2.5.8 Simple FSM 3 (synchronous reset)

weixin_52312830

HDLBits刷题fpga开发算法硬件工程

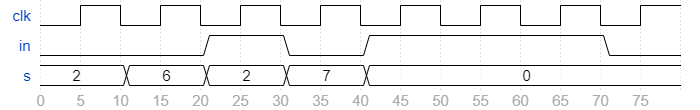

联系3.2.5.5和3.2.5.6来看3.2.5.7SimpleFSM3(asynchronousreset)问题描述下面是一输入一输出四状态的摩尔状态机的状态转移表。实现这个状态机。包括将FSM重置为状态A的异步重置。代码:moduletop_module(inputclk,inputin,inputareset,outputout);//reg[1:0]state,next_state;par

- HDLBits_Verilog刷题笔记Verilog Language Basics(一)

cascleright1

fpga开发硬件架构

前言这个刷题笔记是给自己复习巩固用的,包括自己在刷题的时候遇到的问题,思考,以及看了一些大佬的笔记和答案进行整理和扩充。git开源solutionshttps://github.com/viduraakalanka/HDL-Bits-Solutionsb站up脱发秘籍搬运工,呜呜这个up不管我学什么都有教程,永远也逃不开脱发的世界~https://space.bilibili.com/318808

- USTC Verilog OJ Solutions

Daniel_187

其他fpga开发VerilogHDLrisc-v

科大OJ其对应的英文版:HDLBits刷题网站01输出1moduletop_module(outputone);assignone=1;endmodule02输出0moduletop_module(outputzero);//Modulebodystartsaftersemicolonassignzero=0;endmodule03wiremoduletop_module(inputin,outp

- FPGA快速入门路径

zuoph

FPGA+人工智能电子技术fpga开发硬件工程

适合新手的FPGA入门路径总体路径规划基础学习-verilog语言verilog语言学习,推荐verilog数字系统设计一书,讲解比较详实和全面。练习推荐使用https://hdlbits.01xz.net/,将所有上面例题自己做一遍,便可做到初步掌握硬件设计语言的使用,想要精通还得自己多看多练,尤其是多练。基础学习-数字电路与系统这方面的书很多,推荐数字设计原理与实践一书,简单的过一遍,以后用到

- 「HDLBits题解」CS450

UESTC_KS

HDLBits题解fpga开发Verilog

本专栏的目的是分享可以通过HDLBits仿真的Verilog代码以提供参考各位可同时参考我的代码和官方题解代码或许会有所收益题目链接:Cs450/timer-HDLBitsmoduletop_module(inputclk,inputload,input[9:0]data,outputtc);reg[9:0]cnt;always@(posedgeclk)beginif(load)cnt<=data

- Verilog刷题[hdlbits] :Bcdadd100

卡布达吃西瓜

verilogfpga开发veriloghdlbits

题目:Bcdadd100YouareprovidedwithaBCDone-digitaddernamedbcd_faddthataddstwoBCDdigitsandcarry-in,andproducesasumandcarry-out.为您提供了一个名为bcd_fadd的BCD一位数加法器,它将两个BCD数字相加并带入,并生成一个和和并带入。modulebcd_fadd(input[3:0]

- Verilog刷题[hdlbits] :Adder100i

卡布达吃西瓜

verilogverilogfpga开发hdlbits

题目:Adder100iCreatea100-bitbinaryripple-carryadderbyinstantiating100fulladders.Theadderaddstwo100-bitnumbersandacarry-intoproducea100-bitsumandcarryout.Toencourageyoutoactuallyinstantiatefulladders,als

- 「HDLBits题解」Verification: Writing Testbenches

UESTC_KS

HDLBits题解fpga开发Verilog

本专栏的目的是分享可以通过HDLBits仿真的Verilog代码以提供参考各位可同时参考我的代码和官方题解代码或许会有所收益题目链接:Tb/clock-HDLBits`timescale1ps/1psmoduletop_module();parametertime_period=10;regclk;initialclk=0;alwaysbegin#(time_period/2)clk=~clk;e

- 「HDLBits题解」Build a circuit from a simulation waveform

UESTC_KS

HDLBits题解fpga开发Verilog

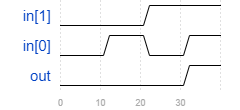

本专栏的目的是分享可以通过HDLBits仿真的Verilog代码以提供参考各位可同时参考我的代码和官方题解代码或许会有所收益题目链接:Sim/circuit1-HDLBitsmoduletop_module(inputa,inputb,outputq);//assignq=a&b;//Fixmeendmodule题目链接:Sim/circuit2-HDLBitsmoduletop_module(i

- 「HDLBits题解」Building Larger Circuits

UESTC_KS

HDLBits题解fpga开发Verilog

本专栏的目的是分享可以通过HDLBits仿真的Verilog代码以提供参考各位可同时参考我的代码和官方题解代码或许会有所收益题目链接:Exams/review2015count1k-HDLBitsmoduletop_module(inputclk,inputreset,output[9:0]q);always@(posedgeclk)beginif(reset)q=0)if(cnt<999)cnt

- 「HDLBits题解」Finite State Machines

UESTC_KS

HDLBits题解fpga开发Verilog

本专栏的目的是分享可以通过HDLBits仿真的Verilog代码以提供参考各位可同时参考我的代码和官方题解代码或许会有所收益题目链接:Fsm1-HDLBitsmoduletop_module(inputclk,inputareset,//AsynchronousresettostateBinputin,outputout);//parameterA=0,B=1;regstate,next_stat

- 【Verilog】HDLBits刷题 03 Verilog语言(2)(未完)

圆喵喵Won

fpga开发

二、模块(module)1.实例化Thefigurebelowshowsaverysimplecircuitwithasub-module.Inthisexercise,createoneinstanceofmodulemod_a,thenconnectthemodule'sthreepins(in1,in2,andout)toyourtop-levelmodule'sthreeports(wir

- 「HDLBits题解」Cellular automata

UESTC_KS

HDLBits题解fpga开发Verilog

本专栏的目的是分享可以通过HDLBits仿真的Verilog代码以提供参考各位可同时参考我的代码和官方题解代码或许会有所收益题目链接:Rule90-HDLBitsmoduletop_module(inputclk,inputload,input[511:0]data,output[511:0]q);always@(posedgeclk)beginif(load)q<=data;elseq<={1'

- 「HDLBits题解」Shift Registers

UESTC_KS

HDLBits题解fpga开发Verilog

本专栏的目的是分享可以通过HDLBits仿真的Verilog代码以提供参考各位可同时参考我的代码和官方题解代码或许会有所收益题目链接:Shift4-HDLBitsmoduletop_module(inputclk,inputareset,//asyncactive-highresettozeroinputload,inputena,input[3:0]data,outputreg[3:0]q);a

- 「HDLBits题解」Latches and Flip-Flops

UESTC_KS

HDLBits题解fpga开发Verilog

本专栏的目的是分享可以通过HDLBits仿真的Verilog代码以提供参考各位可同时参考我的代码和官方题解代码或许会有所收益题目链接:Dff-HDLBitsmoduletop_module(inputclk,//Clocksareusedinsequentialcircuitsinputd,outputregq);////Useaclockedalwaysblock//copydtoqatever

- 「HDLBits题解」Counters

UESTC_KS

HDLBits题解fpga开发Verilog

本专栏的目的是分享可以通过HDLBits仿真的Verilog代码以提供参考各位可同时参考我的代码和官方题解代码或许会有所收益题目链接:Count15-HDLBitsmoduletop_module(inputclk,inputreset,//Synchronousactive-highresetoutput[3:0]q);always@(posedgeclk)beginif(reset)q<=0;

- verilog语法进阶

FPGA中国创新中心

FPGA学习fpga开发verilogfpga硬件工程

文章目录前言一、always块(alwaysblock)二、if语句三、case语句四、casez语句五、三目运算(ternaryconditionaloperator)六、递减运算符(reduction)七、for循环语句八、实例化多个模块(generate)总结前言 本文是针对verilog基础语法做进一步的学,通过网站HDLbits中的代码和例子来展开本文要讨论的内容。HDLbits是一个

- 「HDLBits题解」Popcount255

UESTC_KS

HDLBits题解Verilog

本专栏的目的是分享可以通过HDLBits仿真的Verilog代码以提供参考各位可同时参考我的代码和官方题解代码或许会有所收益题目链接:Popcount255-HDLBitsmoduletop_module(input[254:0]in,outputreg[7:0]out);integeri;always@(*)beginout=0;for(i=0;i>i&1)out=out+1;elseout=o

- 「HDLBits题解」Adder100i

UESTC_KS

HDLBits题解Verilog

本专栏的目的是分享可以通过HDLBits仿真的Verilog代码以提供参考各位可同时参考我的代码和官方题解代码或许会有所收益题目链接:Adder100i-HDLBitsmoduletop_module(input[99:0]a,b,inputcin,output[99:0]cout,output[99:0]sum);add1Add0(a[0],b[0],cin,sum[0],cout[0]);ge

- 「HDLBits题解」Ringer

UESTC_KS

HDLBits题解Verilog

本专栏的目的是分享可以通过HDLBits仿真的Verilog代码以提供参考各位可同时参考我的代码和官方题解代码或许会有所收益题目链接:Ringer-HDLBitsmoduletop_module(inputring,inputvibrate_mode,outputringer,//Makesoundoutputmotor//Vibrate);assignmotor=vibrate_mode?(ri

- 「HDLBits题解」Bcdadd100

UESTC_KS

HDLBits题解Verilog

本专栏的目的是分享可以通过HDLBits仿真的Verilog代码以提供参考各位可同时参考我的代码和官方题解代码或许会有所收益题目链接:Bcdadd100-HDLBitsmoduletop_module(input[399:0]a,b,inputcin,outputcout,output[399:0]sum);wire[99:0]t;genvari;bcd_faddu0(a[3:0],b[3:0],

- 【Verilog】HDLBits题解——Circuits/Sequential Logic

wjh776a68

#Verilog入门verilogHDLBitsfpga

SequentialLogicLatchesandFlip-FlopsDflip-flop题目链接moduletop_module(inputclk,//Clocksareusedinsequentialcircuitsinputd,outputregq);////Useaclockedalwaysblock//copydtoqateverypositiveedgeofclk//Clockedal

- 【Verilog】HDLBits题解——Verilog Language

wjh776a68

#Verilog入门HDLBitsVerilog题解

BasicsSimplewire题目链接moduletop_module(inputin,outputout);assignout=in;endmoduleFourwires题目链接moduletop_module(inputa,b,c,outputw,x,y,z);assignw=a;assignx=b;assigny=b;assignz=c;endmoduleInverter题目链接modul

- 【Verilog】HDLBits题解——Circuits/Combinational Logic

wjh776a68

#Verilog入门VerilogHDLBits题解

CombinationalLogicBasicGatesWire题目链接moduletop_module(inputin,outputout);assignout=in;endmoduleGND题目链接moduletop_module(outputout);assignout=0;endmoduleNOR题目链接moduletop_module(inputin1,inputin2,outputou

- 【Verilog】HDLBits题解——Verification: Writing Testbenches

wjh776a68

#Verilog入门verilogHDLBitsfpga

Clock题目链接moduletop_module();regclk;initialbeginclk=0;forever#5clk=~clk;enddutdut_inst(.clk(clk));endmoduleTestbench1题目链接moduletop_module(outputregA,outputregB);////generateinputpatternshereinitialbegi

- HDLBits Bcdadd100

yezhangyinge

Verilog题解verilog

该题是根据已经写好的十进制加法器(BCDone-digitadder)module来构建100位十进制加法器BCDone-digitadder如下modulebcd_fadd{input[3:0]a,input[3:0]b,inputcin,outputcout,output[3:0]sum);分析显然可以根据二进制的100位加法器的思路,先进行初始化,但是此时我们无法使用简单的寄存器操作来实现功

- HDLbits Conwaylife题目的一种解法

WaterSplash

fpgaverilog

前言最近在刷HDLBits准备今年的提前批和人秋招,目前刷到有限状态机后,发现前面的大部分题目比较基础。目前比较有难度和有意思的题目就是Conwaylife,二维元胞自动机。这里仅提供笔者自己的解法。解题思路比较好想到的方法就是暴力枚举所有情况,给出该情况下所有的相邻坐标。思考过后觉得暴力枚举容易出现遗漏的情况。有没有一种通用的方法可以处理所有坐标呢。参考生命游戏的前两道题,使用另外两个向量,表示

- 「HDLBits题解」Always casez

UESTC_KS

HDLBits题解fpga开发Verilog

本专栏的目的是分享可以通过HDLBits仿真的Verilog代码以提供参考各位可同时参考我的代码和官方题解代码或许会有所收益题目链接:Alwayscasez-HDLBits//synthesisverilog_input_versionverilog_2001moduletop_module(input[7:0]in,outputreg[2:0]pos);always@(*)begincasez(

- 「HDLBits题解」Always nolatches

UESTC_KS

HDLBits题解Verilog

本专栏的目的是分享可以通过HDLBits仿真的Verilog代码以提供参考各位可同时参考我的代码和官方题解代码或许会有所收益题目链接:Alwaysnolatches-HDLBits//synthesisverilog_input_versionverilog_2001moduletop_module(input[15:0]scancode,outputregleft,outputregdown,o

- Hadoop(一)

朱辉辉33

hadooplinux

今天在诺基亚第一天开始培训大数据,因为之前没接触过Linux,所以这次一起学了,任务量还是蛮大的。

首先下载安装了Xshell软件,然后公司给了账号密码连接上了河南郑州那边的服务器,接下来开始按照给的资料学习,全英文的,头也不讲解,说锻炼我们的学习能力,然后就开始跌跌撞撞的自学。这里写部分已经运行成功的代码吧.

在hdfs下,运行hadoop fs -mkdir /u

- maven An error occurred while filtering resources

blackproof

maven报错

转:http://stackoverflow.com/questions/18145774/eclipse-an-error-occurred-while-filtering-resources

maven报错:

maven An error occurred while filtering resources

Maven -> Update Proje

- jdk常用故障排查命令

daysinsun

jvm

linux下常见定位命令:

1、jps 输出Java进程

-q 只输出进程ID的名称,省略主类的名称;

-m 输出进程启动时传递给main函数的参数;

&nb

- java 位移运算与乘法运算

周凡杨

java位移运算乘法

对于 JAVA 编程中,适当的采用位移运算,会减少代码的运行时间,提高项目的运行效率。这个可以从一道面试题说起:

问题:

用最有效率的方法算出2 乘以8 等於几?”

答案:2 << 3

由此就引发了我的思考,为什么位移运算会比乘法运算更快呢?其实简单的想想,计算机的内存是用由 0 和 1 组成的二

- java中的枚举(enmu)

g21121

java

从jdk1.5开始,java增加了enum(枚举)这个类型,但是大家在平时运用中还是比较少用到枚举的,而且很多人和我一样对枚举一知半解,下面就跟大家一起学习下enmu枚举。先看一个最简单的枚举类型,一个返回类型的枚举:

public enum ResultType {

/**

* 成功

*/

SUCCESS,

/**

* 失败

*/

FAIL,

- MQ初级学习

510888780

activemq

1.下载ActiveMQ

去官方网站下载:http://activemq.apache.org/

2.运行ActiveMQ

解压缩apache-activemq-5.9.0-bin.zip到C盘,然后双击apache-activemq-5.9.0-\bin\activemq-admin.bat运行ActiveMQ程序。

启动ActiveMQ以后,登陆:http://localhos

- Spring_Transactional_Propagation

布衣凌宇

springtransactional

//事务传播属性

@Transactional(propagation=Propagation.REQUIRED)//如果有事务,那么加入事务,没有的话新创建一个

@Transactional(propagation=Propagation.NOT_SUPPORTED)//这个方法不开启事务

@Transactional(propagation=Propagation.REQUIREDS_N

- 我的spring学习笔记12-idref与ref的区别

aijuans

spring

idref用来将容器内其他bean的id传给<constructor-arg>/<property>元素,同时提供错误验证功能。例如:

<bean id ="theTargetBean" class="..." />

<bean id ="theClientBean" class=&quo

- Jqplot之折线图

antlove

jsjqueryWebtimeseriesjqplot

timeseriesChart.html

<script type="text/javascript" src="jslib/jquery.min.js"></script>

<script type="text/javascript" src="jslib/excanvas.min.js&

- JDBC中事务处理应用

百合不是茶

javaJDBC编程事务控制语句

解释事务的概念; 事务控制是sql语句中的核心之一;事务控制的作用就是保证数据的正常执行与异常之后可以恢复

事务常用命令:

Commit提交

- [转]ConcurrentHashMap Collections.synchronizedMap和Hashtable讨论

bijian1013

java多线程线程安全HashMap

在Java类库中出现的第一个关联的集合类是Hashtable,它是JDK1.0的一部分。 Hashtable提供了一种易于使用的、线程安全的、关联的map功能,这当然也是方便的。然而,线程安全性是凭代价换来的――Hashtable的所有方法都是同步的。此时,无竞争的同步会导致可观的性能代价。Hashtable的后继者HashMap是作为JDK1.2中的集合框架的一部分出现的,它通过提供一个不同步的

- ng-if与ng-show、ng-hide指令的区别和注意事项

bijian1013

JavaScriptAngularJS

angularJS中的ng-show、ng-hide、ng-if指令都可以用来控制dom元素的显示或隐藏。ng-show和ng-hide根据所给表达式的值来显示或隐藏HTML元素。当赋值给ng-show指令的值为false时元素会被隐藏,值为true时元素会显示。ng-hide功能类似,使用方式相反。元素的显示或

- 【持久化框架MyBatis3七】MyBatis3定义typeHandler

bit1129

TypeHandler

什么是typeHandler?

typeHandler用于将某个类型的数据映射到表的某一列上,以完成MyBatis列跟某个属性的映射

内置typeHandler

MyBatis内置了很多typeHandler,这写typeHandler通过org.apache.ibatis.type.TypeHandlerRegistry进行注册,比如对于日期型数据的typeHandler,

- 上传下载文件rz,sz命令

bitcarter

linux命令rz

刚开始使用rz上传和sz下载命令:

因为我们是通过secureCRT终端工具进行使用的所以会有上传下载这样的需求:

我遇到的问题:

sz下载A文件10M左右,没有问题

但是将这个文件A再传到另一天服务器上时就出现传不上去,甚至出现乱码,死掉现象,具体问题

解决方法:

上传命令改为;rz -ybe

下载命令改为:sz -be filename

如果还是有问题:

那就是文

- 通过ngx-lua来统计nginx上的虚拟主机性能数据

ronin47

ngx-lua 统计 解禁ip

介绍

以前我们为nginx做统计,都是通过对日志的分析来完成.比较麻烦,现在基于ngx_lua插件,开发了实时统计站点状态的脚本,解放生产力.项目主页: https://github.com/skyeydemon/ngx-lua-stats 功能

支持分不同虚拟主机统计, 同一个虚拟主机下可以分不同的location统计.

可以统计与query-times request-time

- java-68-把数组排成最小的数。一个正整数数组,将它们连接起来排成一个数,输出能排出的所有数字中最小的。例如输入数组{32, 321},则输出32132

bylijinnan

java

import java.util.Arrays;

import java.util.Comparator;

public class MinNumFromIntArray {

/**

* Q68输入一个正整数数组,将它们连接起来排成一个数,输出能排出的所有数字中最小的一个。

* 例如输入数组{32, 321},则输出这两个能排成的最小数字32132。请给出解决问题

- Oracle基本操作

ccii

Oracle SQL总结Oracle SQL语法Oracle基本操作Oracle SQL

一、表操作

1. 常用数据类型

NUMBER(p,s):可变长度的数字。p表示整数加小数的最大位数,s为最大小数位数。支持最大精度为38位

NVARCHAR2(size):变长字符串,最大长度为4000字节(以字符数为单位)

VARCHAR2(size):变长字符串,最大长度为4000字节(以字节数为单位)

CHAR(size):定长字符串,最大长度为2000字节,最小为1字节,默认

- [强人工智能]实现强人工智能的路线图

comsci

人工智能

1:创建一个用于记录拓扑网络连接的矩阵数据表

2:自动构造或者人工复制一个包含10万个连接(1000*1000)的流程图

3:将这个流程图导入到矩阵数据表中

4:在矩阵的每个有意义的节点中嵌入一段简单的

- 给Tomcat,Apache配置gzip压缩(HTTP压缩)功能

cwqcwqmax9

apache

背景:

HTTP 压缩可以大大提高浏览网站的速度,它的原理是,在客户端请求网页后,从服务器端将网页文件压缩,再下载到客户端,由客户端的浏览器负责解压缩并浏览。相对于普通的浏览过程HTML ,CSS,Javascript , Text ,它可以节省40%左右的流量。更为重要的是,它可以对动态生成的,包括CGI、PHP , JSP , ASP , Servlet,SHTML等输出的网页也能进行压缩,

- SpringMVC and Struts2

dashuaifu

struts2springMVC

SpringMVC VS Struts2

1:

spring3开发效率高于struts

2:

spring3 mvc可以认为已经100%零配置

3:

struts2是类级别的拦截, 一个类对应一个request上下文,

springmvc是方法级别的拦截,一个方法对应一个request上下文,而方法同时又跟一个url对应

所以说从架构本身上 spring3 mvc就容易实现r

- windows常用命令行命令

dcj3sjt126com

windowscmdcommand

在windows系统中,点击开始-运行,可以直接输入命令行,快速打开一些原本需要多次点击图标才能打开的界面,如常用的输入cmd打开dos命令行,输入taskmgr打开任务管理器。此处列出了网上搜集到的一些常用命令。winver 检查windows版本 wmimgmt.msc 打开windows管理体系结构(wmi) wupdmgr windows更新程序 wscrip

- 再看知名应用背后的第三方开源项目

dcj3sjt126com

ios

知名应用程序的设计和技术一直都是开发者需要学习的,同样这些应用所使用的开源框架也是不可忽视的一部分。此前《

iOS第三方开源库的吐槽和备忘》中作者ibireme列举了国内多款知名应用所使用的开源框架,并对其中一些框架进行了分析,同样国外开发者

@iOSCowboy也在博客中给我们列出了国外多款知名应用使用的开源框架。另外txx's blog中详细介绍了

Facebook Paper使用的第三

- Objective-c单例模式的正确写法

jsntghf

单例iosiPhone

一般情况下,可能我们写的单例模式是这样的:

#import <Foundation/Foundation.h>

@interface Downloader : NSObject

+ (instancetype)sharedDownloader;

@end

#import "Downloader.h"

@implementation

- jquery easyui datagrid 加载成功,选中某一行

hae

jqueryeasyuidatagrid数据加载

1.首先你需要设置datagrid的onLoadSuccess

$(

'#dg'

).datagrid({onLoadSuccess :

function

(data){

$(

'#dg'

).datagrid(

'selectRow'

,3);

}});

2.onL

- jQuery用户数字打分评价效果

ini

JavaScripthtmljqueryWebcss

效果体验:http://hovertree.com/texiao/jquery/5.htmHTML文件代码:

<!DOCTYPE html>

<html xmlns="http://www.w3.org/1999/xhtml">

<head>

<title>jQuery用户数字打分评分代码 - HoverTree</

- mybatis的paramType

kerryg

DAOsql

MyBatis传多个参数:

1、采用#{0},#{1}获得参数:

Dao层函数方法:

public User selectUser(String name,String area);

对应的Mapper.xml

<select id="selectUser" result

- centos 7安装mysql5.5

MrLee23

centos

首先centos7 已经不支持mysql,因为收费了你懂得,所以内部集成了mariadb,而安装mysql的话会和mariadb的文件冲突,所以需要先卸载掉mariadb,以下为卸载mariadb,安装mysql的步骤。

#列出所有被安装的rpm package rpm -qa | grep mariadb

#卸载

rpm -e mariadb-libs-5.

- 利用thrift来实现消息群发

qifeifei

thrift

Thrift项目一般用来做内部项目接偶用的,还有能跨不同语言的功能,非常方便,一般前端系统和后台server线上都是3个节点,然后前端通过获取client来访问后台server,那么如果是多太server,就是有一个负载均衡的方法,然后最后访问其中一个节点。那么换个思路,能不能发送给所有节点的server呢,如果能就

- 实现一个sizeof获取Java对象大小

teasp

javaHotSpot内存对象大小sizeof

由于Java的设计者不想让程序员管理和了解内存的使用,我们想要知道一个对象在内存中的大小变得比较困难了。本文提供了可以获取对象的大小的方法,但是由于各个虚拟机在内存使用上可能存在不同,因此该方法不能在各虚拟机上都适用,而是仅在hotspot 32位虚拟机上,或者其它内存管理方式与hotspot 32位虚拟机相同的虚拟机上 适用。

- SVN错误及处理

xiangqian0505

SVN提交文件时服务器强行关闭

在SVN服务控制台打开资源库“SVN无法读取current” ---摘自网络 写道 SVN无法读取current修复方法 Can't read file : End of file found

文件:repository/db/txn_current、repository/db/current

其中current记录当前最新版本号,txn_current记录版本库中版本