Verilog HDL 复习笔记(二)

编程题

1.设计一个全加器电路,并写出测试代码。

//数据流建模

module ADD1(sum,c_out,A,B,c_in);

input A,B,c_in;

output c_out,sum;

assign sum = (A^B)^c_in;

assign c_out = (A&B)|((A^B)&c_in);

endmodule

module test;

reg A,B,c_in;

wire c_out,sum;

ADD1 ut(sum,c_out,A,B,c_in);

initial

begin

A=1'b0;

B=1'b1;

c_in=1'b0;

#50 A=1'b1;

c_in=1'b1;

#50 B=1'b0;

c_in=1;b0;

end

endmodule

//行为级建模

module ADD1(sum,c_out,A,B,c_in);

output sum,c_out;

input A,B,c_in;

assign {c_out,sum} = A+B+c_in;

endmodule

2.设计一个带复位端且输入时钟clk进行多种分频模块。

设计要求:复位信号为同步、低电平有效,时钟的上升沿触发,要求包括测试电路,并画出仿真波形。

module addr(count,clk,rst,qout);

input clk,rst;

output reg [31:0] count;

always@ (posedge clk)

begin

if(!rst) count = 0;

else count = count+1;

end

assign qout <= count[0];//二分频

endmodule

module test;

reg clk;

reg rst;

addr ut(count,clk,rst);

always #20 clk = ~clk;

initial

begin

clk = 1'b0;

rst = 1'b0;

#20 rst = 1'b1;

end

endmodule3.设计一个奇偶校验位生成电路,输入八位总线信号bus,输出奇校验位odd,偶校验位even。

module parity(even,odd,bus);

output even,odd;

input[7:0] bus; //奇同偶异

assign even = ^bus; //偶校验用异或

assign odd = ^~bus; //奇校验用同或

endmodule4.设计一个带异步复位端、异步置数端(低电平有效)的四位十进制加法计数器,时钟clk上升沿有效,复位信号clr,置数信号load,输入数据data、输出qout。并画出仿真波形图。

module addr_4(qout,clr,clk,load,data);

output reg [3:0] qout;

input[3:0] data;

input load,clr,clk;

always@ (posedge clk or negedge load or negedge clr)

begin

if(clr)

qout<=0;

else if(!load)

qout<=data;

else if(qout<9)

qout<=qout+1;

else

qout = 1'b0;

end

endmodule

module test;

reg clk,clr,load;

reg [3:0] data;

reg [3:0] qout;

addr_4 ut(qout,clr,clk,load,data);

always #10 clk = ~clk;

initial

begin

clk = 0;

clr = 1'b1;

load = 1'b0;

data = 4'b0100;

#20 clr = 1'b0;

#20 load = 1'b1;

clr = 1'b1;

#20 load = 1'b0;

end

endmodule5.数据选择器

//抽象描述方式

//8选1数据选择器

module mux8to1(out,sel,data_in);

output reg out;

input [7:0] data_in;

input [2:0] sel;

always@ (data_in or sel)

case(sel)

3'b000 : out <= data_in[0];

3'b001 : out <= data_in[1];

3'b010 : out <= data_in[2];

3'b011 : out <= data_in[3];

3'b100 : out <= data_in[4];

3'b101 : out <= data_in[5];

3'b110 : out <= data_in[6];

3'b111 : out <= data_in[7];

endcase

endmodule

//4选1数据选择器

module mux4to1(out,sel,data_in);

output reg out;

input [3:0] data_in;

input [1:0] sel;

always@ (data_in or sel)

case(sel)

2'b00 : out <= data_in[0];

2'b01 : out <= data_in[1];

2'b10 : out <= data_in[2];

2'b11 : out <= data_in[3];

endcase

endmodule

6. 任意进制加/减法计数器

对于M进制的计数器,第一步需要确定计数器所需要触发器的个数。N个触发器对应了2^N个状态,应有2^N>M。任意进制计数器选取满足条件的最小N,N为计数器中触发器的个数。

//十一进制加法计数器,反馈清零法

module comp_11(count,clk,rst)

output reg [3:0] count;

input clk,rst;

always@ (posedge clk)

if(rst) count <= 4'b0000; //复位清零

else

if(count == 4'b1010) //计数到10时清零

count <= 1'b0;

else

count <= count+1; //加法计数

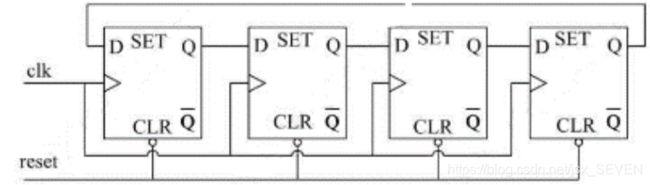

endmodule7.移位寄存器

//4位循环左移

module shiftregist1(Q,clk,reset);

parameter shiftregist_width=4;

output [shiftregist_width-1:0] Q;

input clk,reset;

reg [shiftregist_width-1:0] Q;

always @(posedge clk)

if (!reset)

Q<=4‘b0000;

else

Q<={Q[shiftregist_width-2:0],Q[shiftregist_width-1]};

endmodule8.2输入8位加法器

//行为描述方式

module eight_bits_fulladder(sum,c_out,a,b,c_in)

output [7:0] sum;

output c_out;

input [7:0] a,b;

input c_in;

assign {c_out,sum} = a+b+c_in;

endmodule9.ROM

module rom(dout,clk,addm,cs_n)

input clk,cs_n;

input [2:0] addm;

output reg [7:0] dout;

reg [7:0] rom[7:0];

initial

begin

rom[0] = 8'b0000_0000;

rom[1] = 8'b0000_0001;

rom[2] = 8'b0000_0010;

rom[3] = 8'b0000_0011;

rom[4] = 8'b0000_0100;

rom[5] = 8'b0000_0101;

rom[6] = 8'b0000_0110;

rom[7] = 8'b0000_0111;

end

always@ (posedge clk)

begin

if(cs_n) dout <= 8'bzzzz_zzzz;

else dout <= rom[addm];

end

endmodule

module rom_tb;

reg clk;

reg [2:0] addm;

reg cs_n;

wire [7:0] dout ;

rom PB2(.clk(clk),.addm(addm),.cs_n(cs_n),.dout(dout));

always #10 clk = ~clk;

initial

begin

clk = 0;

addm =0;

cs_n = 0;

end

initial

begin

repeat(7)

#20 addm = addm +1;

end

endmodule10.RAM

module ram(input clk,

input [4:0] addm,

input cs_n,

input we_n,

input [7:0] din,

output reg [7:0]dout);

reg [7:0] ram[31:0];

always @(posedge clk)

begin

if(cs_n) dout <= 8'bzzzz_zzzz;

else

if(we_n) dout <= ram[addm];

else ram[addm] <= din;

end

endmodule

`timescale 1ns/1ps;

module TestRam;

reg clk;

reg [4:0] addm;

reg cs_n;

reg we_n;

reg [7:0] din;

wire [7:0] dout;

ram PB1(.clk(clk),.addm(addm),.cs_n(cs_n),.we_n(we_n),.din(din),.dout(dout));

initial

begin

clk = 0;

addm = 0;

cs_n = 1;

we_n = 0;

din = 0;

#5

cs_n = 0;

#1265

we_n = 1;

end

always #10 clk = ~clk;

initial

begin

repeat(31)

begin

#40 addm = addm +1;

din = din+1;

end

#40 repeat(31)

#40 addm = addm -1;

end

endmodule11.序列检测

//序列检测“111”,moore型

module FSM_moore(input clk,

input rst,

input data,

output result);

parameter ST0 = 4'b000;

parameter ST1 = 4'b001;

parameter ST2 = 4'b010;

parameter ST3 = 4'b100;

reg [3:0] c_state;

reg [3:0] n_state;

always@ (posedge clk)

if(!rst) c_state <= ST0;

else c_state <= n_state;

always@ (c_state,data)

case(c_state)

ST0:

if(data == 1'b1) n_state = ST1;

else n_state = ST0;

ST1:

if(data == 1'b1) n_state = ST2;

else n_state = ST0;

ST2:

if(data == 1'b1) n_state = ST3;

else n_state = ST0;

ST3:

if(data == 1'b1) n_state = ST3

else n_state = ST0;

default: n_state = ST0;

endcase

assign result = (c_state == ST3) ? 1 :0;

endmodule

module FSM_tb;

reg clk,rst,data;

wire moore;

FSM_moore U_moore(.clk(clk),

.rst(rst),

.data(data),

.result(result));

always #10 clk = ~clk;

initial

begin

#0 clk = 1;

rst = 0;

data = 0;

#20 rst = 1'b1;

#20 data = 1'b1;

#20 data = 1'b1;

#20 data = 1'b0;

#20 data = 1'b1;

#20 data = 1'b1;

#20 data = 1'b1;

end

endmodule参考链接 http://www.doc88.com/p-9929960255990.html