- vivado CLOCK_DELAY_GROUP、CLOCK_LOW_FANOUT

cckkppll

fpga开发

CLOCK_DELAY_GROUPLAY_GROUP属性标识具有相同MMCM的相关时钟,PLL、GT源或公共驱动器,应在放置和布线过程中进行平衡减少时钟之间的定时路径上的时钟偏斜。提示:时钟匹配(通过Clock_DELAY_GROUP属性)用于相同的MMCM、PLL或GT源。体系结构支持UltraScale、UltraScale+和VersalACAP体系结构。适用对象•直接连接到全局时钟输出的时

- FPGA实现光纤通信(3)——光纤8b/10b编码数据回环

得之坦然,失之淡然。

FPGA学习笔记fpga开发开源

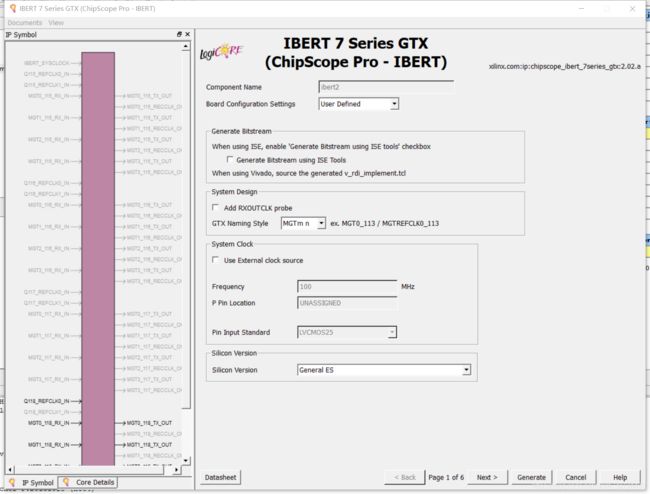

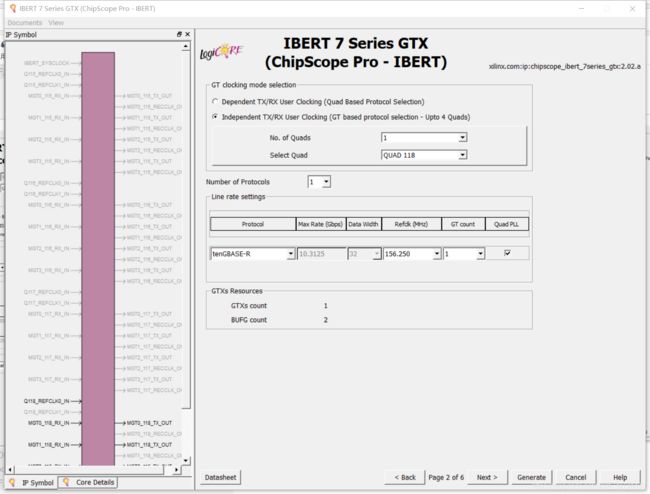

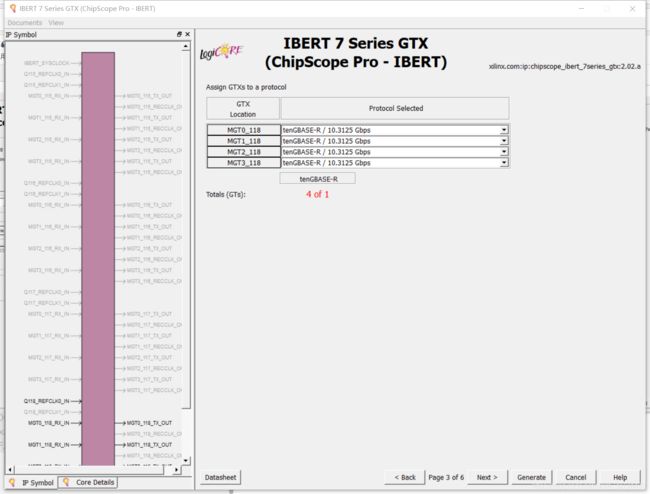

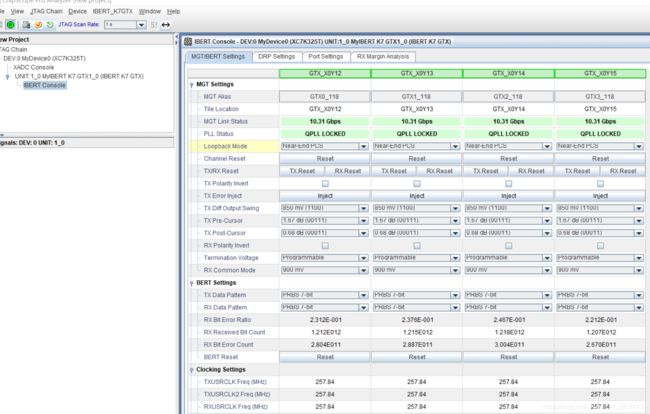

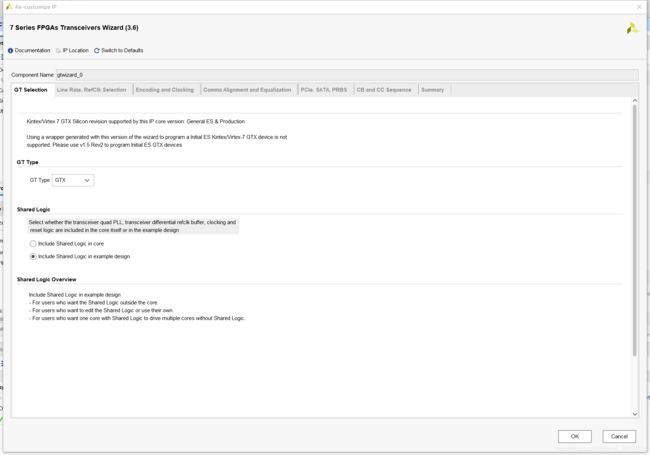

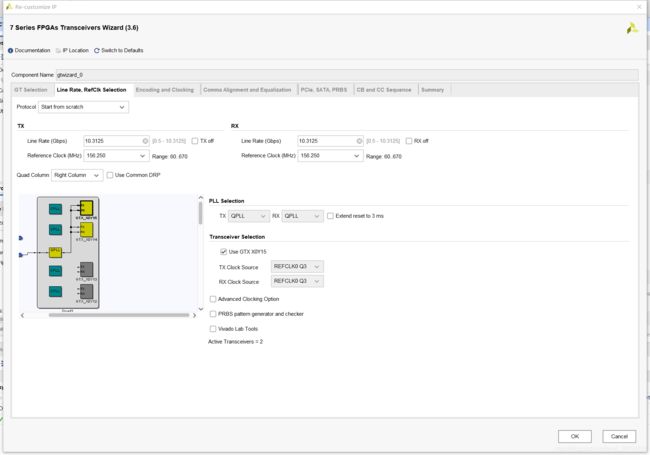

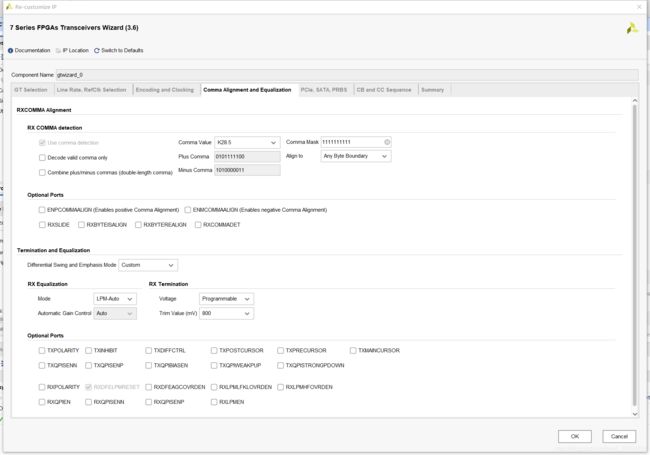

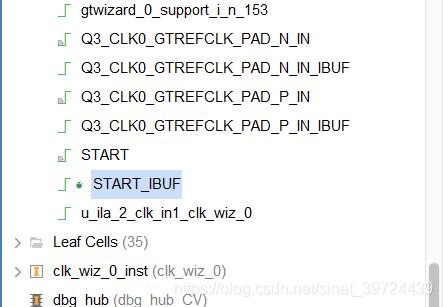

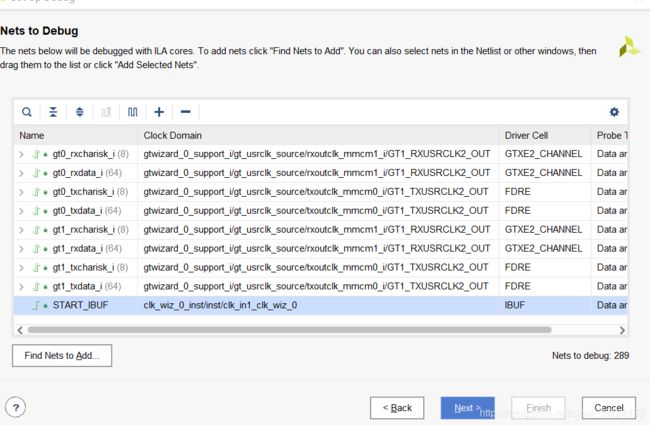

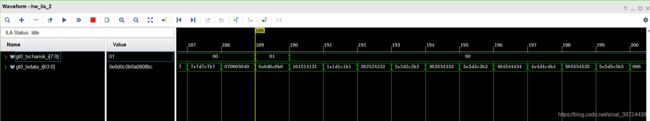

前言光纤通信属于高速串行通信,具有较高的数据传输速率,通常用于服务器以及通信设备之间用于高速数据交换,对于xilinx7系列的FPGA,内部具有集成的高速接口用于实现光纤通信。本次就来实现8b/10b编码数据回环。测试环境:vivado版本:2020.02FPGA芯片:XC7K70T测试说明:进行光纤8B/10B编码数据回环测试8B/10B编码简介8b/10b编码是由IBM公司的Widmer和Fr

- FPGA入门学习之Vivado-数码管驱动设计实验

ZdqDeveloper

fpga开发学习FPGA

在本篇文章中,我们将介绍如何使用Vivado软件进行FPGA的数码管驱动设计实验。数码管是一种常见的输出设备,用于显示数字或字符等信息。通过本实验,您将学习如何使用FPGA来控制数码管的显示,并编写相应的Verilog代码。实验准备:Vivado软件的安装和配置。FPGA开发板(如Xilinx的Basys3)。实验步骤:步骤1:创建新工程打开Vivado软件,并选择"CreateProject"来

- 《基于FPGA的Cortex-M3软核基本SOC设计及外设开发详解》

HWxuYnO

fpga开发程序人生

基于FPGA的Cortex-M3软核基本SOC设计实现基于FPGA的Cortex-M3软核基本SOC,系统外设包括GPIO和UART串口。开发基于vivado2019.2和vitis,理论上可适用于任何版本的vivado,并且附带本人编写的详细开发文档,能够快速完成工程的移植。在该工程基础上可进一步开发更多的功能。ID:42100675319624107小小读者ok基于FPGA的Cortex-M3

- FPGA 时钟树缓存布局布线

cckkppll

fpga开发

时钟树缓存布局布线在以下阶段,Vivado布局器确定MMCM/PLL,全局时钟缓存和时钟根的位置,同时遵守物理XDC约束:1.I/O和时钟布局布局器根据连接规则和用户约束布局I/O缓存和MMCM/PLL。布局器将时钟缓存分配给时钟区域,但不分配给单个site位置,除非使用LOC属性进行约束。只有仅驱动非时钟负载的时钟缓存可以基于它们的驱动器和负载的布局移动到该流程中稍后的不同时钟区域。在此阶段的任

- vivado生成ltx文件命令_实验室自研工具Vivado Batch Mode Tool介绍!

电动星球蟹老板

vivado生成ltx文件命令

这里从两个方面分别进行说明,为什么要使用Vivado的Batchmode。1、流程操作效率我所谓的流程操作效率,是指在使用Vivado时,通过键盘输入、鼠标点击以及进行等待等实际外部操作的效率。例如我需要打开一个Vivado工程,并进行Synthesis,那么在GUI下是这样的流程操作:点击打开VivadoGUI并等待----用Vivado点击打开对应的.xpr文件并等待----点击runSynt

- Verilog中阻塞赋值和非阻塞赋值的区别?

张小侃

数字IC知识fpga硬件

阻塞赋值“=”对应组合逻辑电路赋值(无存储功能,立即赋值),并且会阻塞后面的赋值操作,非阻塞赋值“<=”对应时序逻辑电路赋值(有存储功能),所有非阻塞赋值操作在同一时刻进行赋值。下面分别通过vivado综合不同情况赋值的代码。第一种:在时序逻辑电路中使用阻塞赋值,通过综合后的电路可以看出非阻塞赋值综合出来的电路时立即执行赋值操作,和组合逻辑电路特性一致,无缓存功能,out_o直接被优化掉了。alw

- xilinx vivado PULLMODE 设置思路

坚持每天写程序

fpga开发

1.xilinx引脚分类XilinxIO的分类:以XC7A100TFGG484为例,其引脚分类如下:1.UserIO(用户IO):用户使用的普通IO1.1专用(Dedicated)IO:命名为IO_LXXY_#、IO_XX_#的引脚,有固定的特定用途,多为底层特定功能的直接实现,如差分对信号、关键控制信号等,不能随意变更。1.2多功能(Multi-Function)IO:命名为IO_LXXY_ZZ

- FPGA随记——赛灵思OOC功能

一口一口吃成大V

FPGA随记fpga开发

在这里,我们简要介绍一下Vivado的OOC(Out-of-Context)综合的概念。对于顶层设计,Vivado使用自顶向下的全局(Global)综合方式,将顶层之下的所有逻辑模块都进行综合,但是设置为OOC方式的模块除外,它们独立于顶层设计而单独综合。通常,在整个设计周期中,顶层设计会被多次修改并综合。但有些子模块在创建完毕之后不会因为顶层设计的修改而被修改,如IP,它们被设置为OOC综合方式

- zybo上运行linux,Zybo开发板linux作业系统移植

周行文

zybo上运行linux

文章主要介紹zyboboard上linux作业系统移植过程。分别介绍了开发环境搭建、U-boot编译、linux内核编译、busybox制作等流程及注意事项。文章使用的开发板是zynq7000系列的zyboboard。Vivado版本是2015.1.主机系统是Debian9.1.开发环境搭建工欲善其事必先利其器,做开发前搭建好编译环境是重要的一步,这些步骤大体上都相同,然而对于不同的系统平台、硬件

- 用VCS直接仿真vivado工程

啊节奏不对

vcs仿真fpga开发risc-v嵌入式硬件

用VCS直接仿真vivado工程前言编译vcs仿真库simulation设置RunSimulation写Makefile执行脚本,运行vcs仿真前言在日常搬砖过程中,在ICdesign进行fpga原型验证时,在上fpga测试之前,往往需要对vivado工程进行仿真,而vivado工程中可能存在较多的xilinxip或者blockdesign,直接使用vivado仿真,速度难以接收。如果使用vcs进

- Xilinx Vivado的RTL分析(RTL analysis)、综合(synthesis)和实现

2401_84185145

程序员fpga开发

理论上,FPGA从编程到下载实现预期功能的过程最少仅需要上述7个步骤中的4、5、6和7,即RTL分析、综合、实现和下载。其中的RTL分析、综合、实现的具体含义和区别又是什么?2、RTL分析(RTLanalysis)一般来讲,通常的设计输入都是Verilog、VHDL或者SystemVerilog等硬件描述语言HDL编写的文件,RTL分析这一步就是将HDL语言转化成逻辑电路图的过程。比如HDL语言描

- ARM/Linux嵌入式面经(三二):百度

TrustZone_Hcoco

ARM/Linux嵌入式面试arm开发dubbo芯片嵌入式硬件单片机

文章目录RTOS了解吗,展开讲一下对RTOS的线程和任务管理相关的有了解吗RTOS的线程和任务管理相关了解追问有深度的技术问题及答案vivado这个硬件平台怎么用的Vivado硬件平台使用了解追问有深度的技术问题及答案项目系统架构、配置是怎样的项目系统架构与配置系统架构配置追问有深度的技术问题及答案遇到的难点,怎么解决的?遇到的难点及解决方法追问有深度的技术问题及答案Linux上的异步IO了解过吗

- USER_CROSSING_SLR

cckkppll

fpga开发

在堆叠硅互连(SSI)设备上放置设计元素时,您可以使用要管理的USER_SLR_ASSIGNMENT、USER_CROSSING_SLR和USER_SLL_REG属性逻辑分区和Vivado放置工具的行为。SSI设备由以下部分组成多个超逻辑区域(SLR),由称为超长线的插入器连接连接连接起来(SLL)。有关在单反相机中放置和布线的更多信息,请参阅中的此链接Vivado设计套件的超快设计方法指南(UG

- vivado U_SET

cckkppll

fpga开发

将具有附加相对位置(RLOC)约束的设计元素分组,这些约束是分布在整个设计层次结构中,形成一个集合。U_SET是HDL设计源文件中的一个属性,不会出现在综合或实施的设计。U_SET在定义相对放置宏时使用,或者RTL设计中的RPM。有关使用这些属性和定义的更多信息RPM,请参阅《Vivado设计套件用户指南:使用约束》(UG903)[参考文献19]。而H_SET或HU_SET用于根据设计定义逻辑元素

- 【xilinx】解决vivado中 I/O 时钟布局器错误

神仙约架

xilinxfpga开发时钟vivado时钟布局

典型时钟AMD设备上的典型时钟电路结构如下:输入端口(IBUF)→BUFG→FDCE/C如果使用MMCM或PLL修改时钟,则其结构如下:输入端口(IBUF)→BUFG→MMCM/PLL→BUFG→FDCE/C对于GT时钟,其结构如下:GT_QUAD→BUFG_GT→FDCE/CI/O时钟布局阶段可能会发生错误,表明该工具无法放置时钟结构直到最后一个BUFG。分析发生这种情况的原因可能有多种:时钟结

- 超详细的 Vivado 2021.1 安装教程(适合新手)

shuai_258

Vivado2021.1c++人工智能fpga开发

Vivado是Xilinx推出的FPGA和SoC设计工具。对于新手来说,安装和配置Vivado可能有些复杂,因此本文将详细讲解每一个步骤,并介绍如何免费激活Vivado。1.系统要求确保你的电脑满足以下要求:操作系统:Windows:Windows1064-bitLinux:CentOS7.x/8.x,RedHat7.x/8.x,Ubuntu18.04/20.04内存:16GB(最低8GB)硬盘空

- vivado SLEW

cckkppll

fpga开发

SLEW为配置了I/O标准的输出缓冲区指定了输出缓冲区转换速率支持可编程输出转换速率。架构支持所有架构。适用对象•端口(get_Ports)°连接输出或双向端口•单元(get_cell)°输出缓冲器(所有OBUF变体)价值观•慢速(默认)•中等:适用于UltraScale体系结构,仅适用于高性能(HP)I/O。•快速SyntaxVerilogSyntaxTosetthisattributewhen

- Vitis/Vivado HLS 流水线中的存储依赖——解决方法之二

优质蛋白 - 芯片打工人

高层次综合HLSfpga开发经验分享fpga嵌入式硬件

和上一篇内容Vitis/VivadoHLS流水线中的存储依赖——解决方法之一中一样,考虑以下函数模块,voidExampleModule(hls::streamstrm_in,hls::streamstrm_out){#pragmaHLSINTERFACEmode=ap_ctrl_noneport=returnt_datamem[2*N];#pragmaHLSBIND_STORAGEvariabl

- vivado RPM

cckkppll

fpga开发

RPM属性是分配给定义集的逻辑元素的只读属性通过RTL源文件中的H_SET、HU_SET或U_SET属性。当RTL源文件中也存在RLOC时,H_SET、HU_SET和U_SET属性转换为合成网表中单元格的只读RPM属性。HU_SET在VivadoDesign的文本编辑器中的RTL源文件上可以看到U_SET属性一套。但是,在单元格对象的“属性”窗口中,会显示RPM属性。For有关使用这些属性和定义R

- (135)vivado综合选项--->(35)Vivado综合策略三五

FPGA系统设计指南针

数字IC系统设计(提升笔记)单片机嵌入式硬件FPGA综合

1目录(a)IC简介(b)数字IC设计流程(c)Verilog简介(d)Vivado综合策略三五(e)结束1IC简介(a)在IC设计中,设计师使用电路设计工具(如EDA软件)来设计和模拟各种电路,例如逻辑电路、模拟电路、数字信号处理电路等。然后,根据设计电路的规格要求,进行布局设计和布线,确定各个电路元件的位置和连线方式。最后,进行物理设计,考虑电磁兼容性、功耗优化、时序等问题,并生成芯片制造所需

- RLOC_ORIGIN

cckkppll

fpga开发

RLOC_ORIGIN属性为相对放置的对象提供绝对位置或LOCRTL设计中的宏(RPM)。有关定义RPM和使用RLOC_ORIGIN属性,请参阅《VivadoDesignSuite用户指南:使用约束》(UG903)[参考文献19]。RPM是通过使用H_set、HU_set或U_set将设计元素分配给集合来定义的RTL设计中的优点。然后,为设计元素分配一个相对位置彼此使用RLOC属性。您可以定义任何

- (134)vivado综合选项--->(34)Vivado综合策略三四

FPGA系统设计指南针

数字IC系统设计(提升笔记)单片机嵌入式硬件FPGA综合

1目录(a)IC简介(b)数字IC设计流程(c)Verilog简介(d)Vivado综合策略三四(e)结束1IC简介(a)在IC设计中,设计师使用电路设计工具(如EDA软件)来设计和模拟各种电路,例如逻辑电路、模拟电路、数字信号处理电路等。然后,根据设计电路的规格要求,进行布局设计和布线,确定各个电路元件的位置和连线方式。最后,进行物理设计,考虑电磁兼容性、功耗优化、时序等问题,并生成芯片制造所需

- 【vivado】fpga时钟信号引入

刘小适

日拱一卒XilinxSoCFPGAfpga开发

FPGA的时钟信号一般由板上晶振经由时钟引脚引入,有时由于工程需要也会从pin脚引入其他外部时钟,这时为了该时钟能够正常工作,满足xilinxfpga的外部时钟引入规则。一、从专用的MRCC/SRCC时钟引脚引入对于XilinxFPGA来说必须使用片上的MRCC或者SRCC引脚来把外部时钟信号引入FPGA、添加相关的时钟约束,然后再在FPGA上使用这些引入的时钟。二、从其他IO引入外部时钟如果设计

- xilinx FPGA 除法器IP核(divider)的使用 vivado 2019.1

小 阿 飞

fpga开发

参考:xilinxFPGA除法器ip核(divider)的使用(VHDL&Vivado)_vivado除法器_坚持每天写程序的博客-CSDN博客一、创建除法IPvivado的除法器ip核有三种类型,跟ISE相比多了一个LuMult类型,总结来说就是LuMult:使用了DSP切片、块RAM和少量的FPGA逻辑原语(寄存器和lut),所以和Radix2相比占用fpga资源更少;可以选择有符号或者无符号

- 除法器 c语言 模拟,用Vivado-HLS实现低latency除法器

小小羊羊羊

除法器c语言模拟

GeorgeWang–XilinxDSPSpecialist1VivadoHLS简介XilinxVivadoHigh-LevelSynthesis(HLS)工具将C,C++,或者SystemC设计规范,算法转成RegisterTransferLevel(RTL)实现,可综合到XilinxFPGA。将DSP算法快速转到RTLFPGA实现将C至RTL时间缩短4倍基于C语言的验证时间缩短100倍RTL仿

- xilinx除法器的使用

爱漂流的易子

xilinx的各类ip的使用fpga开发

平台:Vivado2018.3.芯片:xcku115-flva1517-2-i(active)最近学习使用了xilinx除法器,在使用过程中出现了很多次除法器的结果和我预计的结果不一致,特此记录学习一下。参考文件:pg151.下载地址pg151-div-gen.pdf•查看器•AMD自适应计算文档门户(xilinx.com)IP配置说明Xilinx除法器拥有三种模式Radix2:Theimplem

- 硬件加速OpenCV的图像处理方法研究

Jason_儿

摘要:研究了一种基于VivadoHLS加速OpenCV程序的方法,其核心是利用Xilinx高层次综合工具VivadoHLS,将C++编写的OpenCV程序按照VivadoHLS处理规范进行修改,进而将代码转换为硬件描述语言,可快速生成IP核。结合XilinxZynqSoC架构和其视频图像处理方面的优势,通过软硬件协同的方法,实现OpenCV程序算法向高性能处理平台ZynqSoC系统的移植和加速。该

- FPGA时钟资源与设计方法——IO延迟约束(Vivado)

CWNULT

fpga开发

目录1I/O延迟约束简介2IO约束指令3输入延迟(InputDelay)4输出延迟(OutputDelay)1I/O延迟约束简介Vivado对整个工程的时序进行分析时,只能分析内部的时序信息,对于外部的时序信息Vivado无法提供,在设计中要精确建模外部时序信息,必须为输入和输出端口提供输入输出延迟信息,而I/O延迟约束就是告知XilinxVivado集成设计环境(IDE)FPGA管脚外部的输入输

- vivado DSP Block

cckkppll

fpga开发

当对推理进行编码并以DSP块为目标时,建议使用签名算术运算,并且要求预加器结果有一个额外的宽度位,以便可以打包到DSP块中。Pre-AdderDynamicallyConfiguredFollowedbyMultiplierandPost-Adder(Verilog)Filename:dynpreaddmultadd.v//Pre-add/subtractselectwithDynamiccont

- 数据采集高并发的架构应用

3golden

.net

问题的出发点:

最近公司为了发展需要,要扩大对用户的信息采集,每个用户的采集量估计约2W。如果用户量增加的话,将会大量照成采集量成3W倍的增长,但是又要满足日常业务需要,特别是指令要及时得到响应的频率次数远大于预期。

&n

- 不停止 MySQL 服务增加从库的两种方式

brotherlamp

linuxlinux视频linux资料linux教程linux自学

现在生产环境MySQL数据库是一主一从,由于业务量访问不断增大,故再增加一台从库。前提是不能影响线上业务使用,也就是说不能重启MySQL服务,为了避免出现其他情况,选择在网站访问量低峰期时间段操作。

一般在线增加从库有两种方式,一种是通过mysqldump备份主库,恢复到从库,mysqldump是逻辑备份,数据量大时,备份速度会很慢,锁表的时间也会很长。另一种是通过xtrabacku

- Quartz——SimpleTrigger触发器

eksliang

SimpleTriggerTriggerUtilsquartz

转载请出自出处:http://eksliang.iteye.com/blog/2208166 一.概述

SimpleTrigger触发器,当且仅需触发一次或者以固定时间间隔周期触发执行;

二.SimpleTrigger的构造函数

SimpleTrigger(String name, String group):通过该构造函数指定Trigger所属组和名称;

Simpl

- Informatica应用(1)

18289753290

sqlworkflowlookup组件Informatica

1.如果要在workflow中调用shell脚本有一个command组件,在里面设置shell的路径;调度wf可以右键出现schedule,现在用的是HP的tidal调度wf的执行。

2.designer里面的router类似于SSIS中的broadcast(多播组件);Reset_Workflow_Var:参数重置 (比如说我这个参数初始是1在workflow跑得过程中变成了3我要在结束时还要

- python 获取图片验证码中文字

酷的飞上天空

python

根据现成的开源项目 http://code.google.com/p/pytesser/改写

在window上用easy_install安装不上 看了下源码发现代码很少 于是就想自己改写一下

添加支持网络图片的直接解析

#coding:utf-8

#import sys

#reload(sys)

#sys.s

- AJAX

永夜-极光

Ajax

1.AJAX功能:动态更新页面,减少流量消耗,减轻服务器负担

2.代码结构:

<html>

<head>

<script type="text/javascript">

function loadXMLDoc()

{

.... AJAX script goes here ...

- 创业OR读研

随便小屋

创业

现在研一,有种想创业的想法,不知道该不该去实施。因为对于的我情况这两者是矛盾的,可能就是鱼与熊掌不能兼得。

研一的生活刚刚过去两个月,我们学校主要的是

- 需求做得好与坏直接关系着程序员生活质量

aijuans

IT 生活

这个故事还得从去年换工作的事情说起,由于自己不太喜欢第一家公司的环境我选择了换一份工作。去年九月份我入职现在的这家公司,专门从事金融业内软件的开发。十一月份我们整个项目组前往北京做现场开发,从此苦逼的日子开始了。

系统背景:五月份就有同事前往甲方了解需求一直到6月份,后续几个月也完

- 如何定义和区分高级软件开发工程师

aoyouzi

在软件开发领域,高级开发工程师通常是指那些编写代码超过 3 年的人。这些人可能会被放到领导的位置,但经常会产生非常糟糕的结果。Matt Briggs 是一名高级开发工程师兼 Scrum 管理员。他认为,单纯使用年限来划分开发人员存在问题,两个同样具有 10 年开发经验的开发人员可能大不相同。近日,他发表了一篇博文,根据开发者所能发挥的作用划分软件开发工程师的成长阶段。

初

- Servlet的请求与响应

百合不是茶

servletget提交java处理post提交

Servlet是tomcat中的一个重要组成,也是负责客户端和服务端的中介

1,Http的请求方式(get ,post);

客户端的请求一般都会都是Servlet来接受的,在接收之前怎么来确定是那种方式提交的,以及如何反馈,Servlet中有相应的方法, http的get方式 servlet就是都doGet(

- web.xml配置详解之listener

bijian1013

javaweb.xmllistener

一.定义

<listener>

<listen-class>com.myapp.MyListener</listen-class>

</listener>

二.作用 该元素用来注册一个监听器类。可以收到事件什么时候发生以及用什么作为响

- Web页面性能优化(yahoo技术)

Bill_chen

JavaScriptAjaxWebcssYahoo

1.尽可能的减少HTTP请求数 content

2.使用CDN server

3.添加Expires头(或者 Cache-control) server

4.Gzip 组件 server

5.把CSS样式放在页面的上方。 css

6.将脚本放在底部(包括内联的) javascript

7.避免在CSS中使用Expressions css

8.将javascript和css独立成外部文

- 【MongoDB学习笔记八】MongoDB游标、分页查询、查询结果排序

bit1129

mongodb

游标

游标,简单的说就是一个查询结果的指针。游标作为数据库的一个对象,使用它是包括

声明

打开

循环抓去一定数目的文档直到结果集中的所有文档已经抓取完

关闭游标

游标的基本用法,类似于JDBC的ResultSet(hasNext判断是否抓去完,next移动游标到下一条文档),在获取一个文档集时,可以提供一个类似JDBC的FetchSize

- ORA-12514 TNS 监听程序当前无法识别连接描述符中请求服务 的解决方法

白糖_

ORA-12514

今天通过Oracle SQL*Plus连接远端服务器的时候提示“监听程序当前无法识别连接描述符中请求服务”,遂在网上找到了解决方案:

①打开Oracle服务器安装目录\NETWORK\ADMIN\listener.ora文件,你会看到如下信息:

# listener.ora Network Configuration File: D:\database\Oracle\net

- Eclipse 问题 A resource exists with a different case

bozch

eclipse

在使用Eclipse进行开发的时候,出现了如下的问题:

Description Resource Path Location TypeThe project was not built due to "A resource exists with a different case: '/SeenTaoImp_zhV2/bin/seentao'.&

- 编程之美-小飞的电梯调度算法

bylijinnan

编程之美

public class AptElevator {

/**

* 编程之美 小飞 电梯调度算法

* 在繁忙的时间,每次电梯从一层往上走时,我们只允许电梯停在其中的某一层。

* 所有乘客都从一楼上电梯,到达某层楼后,电梯听下来,所有乘客再从这里爬楼梯到自己的目的层。

* 在一楼时,每个乘客选择自己的目的层,电梯则自动计算出应停的楼层。

* 问:电梯停在哪

- SQL注入相关概念

chenbowen00

sqlWeb安全

SQL Injection:就是通过把SQL命令插入到Web表单递交或输入域名或页面请求的查询字符串,最终达到欺骗服务器执行恶意的SQL命令。

具体来说,它是利用现有应用程序,将(恶意)的SQL命令注入到后台数据库引擎执行的能力,它可以通过在Web表单中输入(恶意)SQL语句得到一个存在安全漏洞的网站上的数据库,而不是按照设计者意图去执行SQL语句。

首先让我们了解什么时候可能发生SQ

- [光与电]光子信号战防御原理

comsci

原理

无论是在战场上,还是在后方,敌人都有可能用光子信号对人体进行控制和攻击,那么采取什么样的防御方法,最简单,最有效呢?

我们这里有几个山寨的办法,可能有些作用,大家如果有兴趣可以去实验一下

根据光

- oracle 11g新特性:Pending Statistics

daizj

oracledbms_stats

oracle 11g新特性:Pending Statistics 转

从11g开始,表与索引的统计信息收集完毕后,可以选择收集的统信息立即发布,也可以选择使新收集的统计信息处于pending状态,待确定处于pending状态的统计信息是安全的,再使处于pending状态的统计信息发布,这样就会避免一些因为收集统计信息立即发布而导致SQL执行计划走错的灾难。

在 11g 之前的版本中,D

- 快速理解RequireJs

dengkane

jqueryrequirejs

RequireJs已经流行很久了,我们在项目中也打算使用它。它提供了以下功能:

声明不同js文件之间的依赖

可以按需、并行、延时载入js库

可以让我们的代码以模块化的方式组织

初看起来并不复杂。 在html中引入requirejs

在HTML中,添加这样的 <script> 标签:

<script src="/path/to

- C语言学习四流程控制if条件选择、for循环和强制类型转换

dcj3sjt126com

c

# include <stdio.h>

int main(void)

{

int i, j;

scanf("%d %d", &i, &j);

if (i > j)

printf("i大于j\n");

else

printf("i小于j\n");

retu

- dictionary的使用要注意

dcj3sjt126com

IO

NSDictionary *dict = [NSDictionary dictionaryWithObjectsAndKeys:

user.user_id , @"id",

user.username , @"username",

- Android 中的资源访问(Resource)

finally_m

xmlandroidStringdrawablecolor

简单的说,Android中的资源是指非代码部分。例如,在我们的Android程序中要使用一些图片来设置界面,要使用一些音频文件来设置铃声,要使用一些动画来显示特效,要使用一些字符串来显示提示信息。那么,这些图片、音频、动画和字符串等叫做Android中的资源文件。

在Eclipse创建的工程中,我们可以看到res和assets两个文件夹,是用来保存资源文件的,在assets中保存的一般是原生

- Spring使用Cache、整合Ehcache

234390216

springcacheehcache@Cacheable

Spring使用Cache

从3.1开始,Spring引入了对Cache的支持。其使用方法和原理都类似于Spring对事务管理的支持。Spring Cache是作用在方法上的,其核心思想是这样的:当我们在调用一个缓存方法时会把该方法参数和返回结果作为一个键值对存放在缓存中,等到下次利用同样的

- 当druid遇上oracle blob(clob)

jackyrong

oracle

http://blog.csdn.net/renfufei/article/details/44887371

众所周知,Oracle有很多坑, 所以才有了去IOE。

在使用Druid做数据库连接池后,其实偶尔也会碰到小坑,这就是使用开源项目所必须去填平的。【如果使用不开源的产品,那就不是坑,而是陷阱了,你都不知道怎么去填坑】

用Druid连接池,通过JDBC往Oracle数据库的

- easyui datagrid pagination获得分页页码、总页数等信息

ldzyz007

var grid = $('#datagrid');

var options = grid.datagrid('getPager').data("pagination").options;

var curr = options.pageNumber;

var total = options.total;

var max =

- 浅析awk里的数组

nigelzeng

二维数组array数组awk

awk绝对是文本处理中的神器,它本身也是一门编程语言,还有许多功能本人没有使用到。这篇文章就单单针对awk里的数组来进行讨论,如何利用数组来帮助完成文本分析。

有这么一组数据:

abcd,91#31#2012-12-31 11:24:00

case_a,136#19#2012-12-31 11:24:00

case_a,136#23#2012-12-31 1

- 搭建 CentOS 6 服务器(6) - TigerVNC

rensanning

centos

安装GNOME桌面环境

# yum groupinstall "X Window System" "Desktop"

安装TigerVNC

# yum -y install tigervnc-server tigervnc

启动VNC服务

# /etc/init.d/vncserver restart

# vncser

- Spring 数据库连接整理

tomcat_oracle

springbeanjdbc

1、数据库连接jdbc.properties配置详解 jdbc.url=jdbc:hsqldb:hsql://localhost/xdb jdbc.username=sa jdbc.password= jdbc.driver=不同的数据库厂商驱动,此处不一一列举 接下来,详细配置代码如下:

Spring连接池

- Dom4J解析使用xpath java.lang.NoClassDefFoundError: org/jaxen/JaxenException异常

xp9802

用Dom4J解析xml,以前没注意,今天使用dom4j包解析xml时在xpath使用处报错

异常栈:java.lang.NoClassDefFoundError: org/jaxen/JaxenException异常

导入包 jaxen-1.1-beta-6.jar 解决;

&nb