or1200的soc完善

现在这个or1200_basic_soc还是很单调的hor!

既然这样就去opencores上看看有什么资源搜刮咯~

·····

现在的SOC只有CPU、RAM、UART、BUS、DEBUG

一个极端的例子,CPU只要有GPIO Controler就可以控制一切的外设了,虽然这样比较极端,会花大量的CPU资源对外设做时序操作,CPU的效率会严重降低,这就是为什么要加外设控制器的原因。

在opencores社区上找到自己喜欢的就download吧,至于后面移植u-boot来说,建议有ethernet,这样的话调试就很方便了,但是至少还有一个能固化程序的存储器,或者是Flash,或者是SD卡。

好吧,对于这个SOC来说,我们现在只要40M的or1200,想想加些什么外设控制器进去吧,尽量地加,GPIO、Ethernet、SD/MMC、FLASH、I2C、SPI、USB、VGA、DMA、AC97······

下一步想按照opencores社区提供的教程把u-boot移植到板子上,所以这里我只选择添加两个控制器,FLASH和Ethernet,如果没有FLASH的话就选择SD/MMC,如果都没有的话,后面就比较麻烦了,就算调试完的程序每次都要从虚拟机中下载到板子。

所以,利用我手头上的板子的flash芯片咯,至于在opencores上又关于CFI接口flash的ipcore,cfi_ctrl_latest.tar.gz,这个ipcore把软件上的CFI驱动也综合到硬件中,使得读写flash象读写ram一样简单,但是关于包括读操作、写操作、擦出操作等等都要自己手动去编写,所以想后面为了省点事,不去写基于cfi_ctrl_latest.tar.gz这个ipcore的驱动代码,就自己做个flash的wishbone接口,挂到bus上,这样就象操作通用的gpio口一样,这样就可以直接使用u-boot和linux中的cfi驱动。

至于wishbone总线的关于器件的接口如何去写,先认真读读《开源软核处理器OPENRISC的SOPC设计》、《CPU源代码分析与芯片设计及Linux移植》这两本书关于wishbone总线的概念,然后《CPU源代码分析与芯片设计及Linux移植》第3章最后一节中有介绍如何编写一个wishbone接口,并且在

minsoc_latest.tar.gz

or1k_soc_on_altera_embedded_dev_kit_latest.tar

orpsoc-master.tar.gz

这三个参考的SOC工程中都有wb接口关于ram的例子,可以参考着写,这里就不详述了,附件中会上传我板子flash芯片的接口代码,型号是JS28F640J3D75,16bit,附件中把例子和原理图都上传。

对于16bit的flash来说,cpu取指是32bit的,所以在接口的操作中要连续读取flash然后拼接成32bit的数据,写操作也一样,要将32bit数据拆分成word-byte,如果板子上flash是8bit或者级联成32bit的稍微改改程序就ok了,程序很简单,一个三段式的状态机控制读写时序和操作。

如果板子是spi serial flash的话,orpsoc-master.tar.gz里面有基于spi的驱动代码和相关的测试代码,在opencores上下载simple_spi_latest.tar.gz源码包,自行添加到SOC上,ORPSOCv2的SW目录下有基于spi时序读写serial flash的代码,然后自己根据自己的开发板想想办法解决咯。

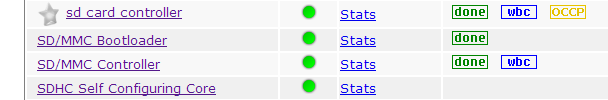

对于板子没有flash但是又SD/MMC接口的话可以尝试用SD卡来固化程序spimaster_latest.tar.gz这个ipcore是基于spi总线的SD卡控制器,在opencores社区上SD/MMC controllerproject下。

or1k_soc_on_altera_embedded_dev_kit_latest.tar这个参考SOC设计中有该控制器的驱动代码,是大虾Xianfeng Zeng写的,可以自己去理解理解,因为这个SD/MMC控制器已经屏蔽SD卡读写的SPI时序和命令,使得读写SD卡像读写RAM一样简单,所以代码很容易理解。

再或者说你的FPGA芯片里的资源多得无法想象,把ROM做在FPGA里面吧,不过应该没人会这样干的。

OK,存储器这里就差不多了,接下来就是ethernet。

学计算机网络的时候就知道网络最下面两层分别是物理层和数据链路层,数据链路层又分开LLC层和MAC层,而关于板卡网络芯片的形式普遍有两种。

第一种是CPU内有MAC控制器,但是没有物理层的传输接口,在板卡上加PHY芯片,一个RJ45接口构成,比如说某些主板上独立的Realtek 8XXX就是一块PHY芯片,通过南桥芯片集成的MAC控制器完成处理。

第二种就是讲MAC和PHY集成在一块芯片内,常见如DM9000和CS8900。

例如我的板子上有一块DM9000,所以就不用在or1200上集成一个MAC控制器,但是要为DM9000的网络编写一个wishbone接口或者添加一个GPIO模块控制DM9000,由于前面有编写RAM和Flash的wishbone接口的经验,这里选择为DM9000编写一个wishbone接口的方式。

如果板子上的是PHY芯片的话,就要在CPU内自行添加一个MAC控制器,所以上opencores上的Ethernet MAC 10/100 Mbpsproject下载MAC控制器,添加到or1200上,至于代码可以参考ORPSOCv2,这个SOC的网络部分就是用这个ipcore实现的,而至于驱动代码opencores社区的大牛们都写好了,在u-boot和linux的源码中都有该驱动代码,在移植u-boot的时候如果选择用的是Ethernet MAC10/100 Mbps的话就直接可以上了。

那废话少说吧,资源一栏附件中会上传我自己根据板子搭建SOC使用的所有ipcores和工程源码,命名为or1200_soc,用的quartusii9.1编译,有兴趣的可以参考下,大侠们路过就不要吐槽了,搭建好了下面我们跟着opencores社区的大侠写的移植u-boot教程和参考ARM技术交流网推出《u-boot移植手册》把u-boot移植到自己搭建的SOC上。