- HDLBits刷题Day23,3.2.5.7 Simple FSM 3 (asynchronous reset) - 3.2.5.8 Simple FSM 3 (synchronous reset)

weixin_52312830

HDLBits刷题fpga开发算法硬件工程

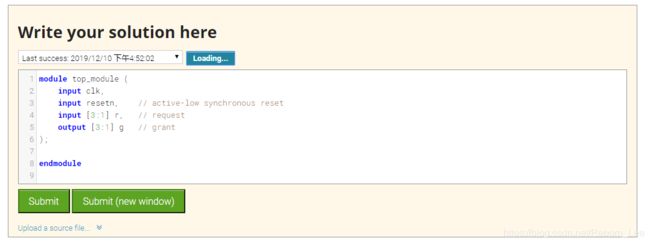

联系3.2.5.5和3.2.5.6来看3.2.5.7SimpleFSM3(asynchronousreset)问题描述下面是一输入一输出四状态的摩尔状态机的状态转移表。实现这个状态机。包括将FSM重置为状态A的异步重置。代码:moduletop_module(inputclk,inputin,inputareset,outputout);//reg[1:0]state,next_state;par

- HDLBits_Verilog刷题笔记Verilog Language Basics(一)

cascleright1

fpga开发硬件架构

前言这个刷题笔记是给自己复习巩固用的,包括自己在刷题的时候遇到的问题,思考,以及看了一些大佬的笔记和答案进行整理和扩充。git开源solutionshttps://github.com/viduraakalanka/HDL-Bits-Solutionsb站up脱发秘籍搬运工,呜呜这个up不管我学什么都有教程,永远也逃不开脱发的世界~https://space.bilibili.com/318808

- USTC Verilog OJ Solutions

Daniel_187

其他fpga开发VerilogHDLrisc-v

科大OJ其对应的英文版:HDLBits刷题网站01输出1moduletop_module(outputone);assignone=1;endmodule02输出0moduletop_module(outputzero);//Modulebodystartsaftersemicolonassignzero=0;endmodule03wiremoduletop_module(inputin,outp

- FPGA快速入门路径

zuoph

FPGA+人工智能电子技术fpga开发硬件工程

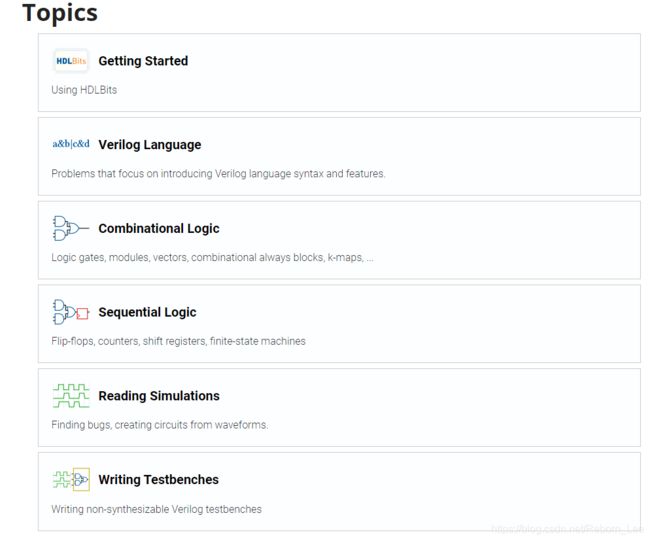

适合新手的FPGA入门路径总体路径规划基础学习-verilog语言verilog语言学习,推荐verilog数字系统设计一书,讲解比较详实和全面。练习推荐使用https://hdlbits.01xz.net/,将所有上面例题自己做一遍,便可做到初步掌握硬件设计语言的使用,想要精通还得自己多看多练,尤其是多练。基础学习-数字电路与系统这方面的书很多,推荐数字设计原理与实践一书,简单的过一遍,以后用到

- 「HDLBits题解」CS450

UESTC_KS

HDLBits题解fpga开发Verilog

本专栏的目的是分享可以通过HDLBits仿真的Verilog代码以提供参考各位可同时参考我的代码和官方题解代码或许会有所收益题目链接:Cs450/timer-HDLBitsmoduletop_module(inputclk,inputload,input[9:0]data,outputtc);reg[9:0]cnt;always@(posedgeclk)beginif(load)cnt<=data

- Verilog刷题[hdlbits] :Bcdadd100

卡布达吃西瓜

verilogfpga开发veriloghdlbits

题目:Bcdadd100YouareprovidedwithaBCDone-digitaddernamedbcd_faddthataddstwoBCDdigitsandcarry-in,andproducesasumandcarry-out.为您提供了一个名为bcd_fadd的BCD一位数加法器,它将两个BCD数字相加并带入,并生成一个和和并带入。modulebcd_fadd(input[3:0]

- Verilog刷题[hdlbits] :Adder100i

卡布达吃西瓜

verilogverilogfpga开发hdlbits

题目:Adder100iCreatea100-bitbinaryripple-carryadderbyinstantiating100fulladders.Theadderaddstwo100-bitnumbersandacarry-intoproducea100-bitsumandcarryout.Toencourageyoutoactuallyinstantiatefulladders,als

- 「HDLBits题解」Verification: Writing Testbenches

UESTC_KS

HDLBits题解fpga开发Verilog

本专栏的目的是分享可以通过HDLBits仿真的Verilog代码以提供参考各位可同时参考我的代码和官方题解代码或许会有所收益题目链接:Tb/clock-HDLBits`timescale1ps/1psmoduletop_module();parametertime_period=10;regclk;initialclk=0;alwaysbegin#(time_period/2)clk=~clk;e

- 「HDLBits题解」Build a circuit from a simulation waveform

UESTC_KS

HDLBits题解fpga开发Verilog

本专栏的目的是分享可以通过HDLBits仿真的Verilog代码以提供参考各位可同时参考我的代码和官方题解代码或许会有所收益题目链接:Sim/circuit1-HDLBitsmoduletop_module(inputa,inputb,outputq);//assignq=a&b;//Fixmeendmodule题目链接:Sim/circuit2-HDLBitsmoduletop_module(i

- 「HDLBits题解」Building Larger Circuits

UESTC_KS

HDLBits题解fpga开发Verilog

本专栏的目的是分享可以通过HDLBits仿真的Verilog代码以提供参考各位可同时参考我的代码和官方题解代码或许会有所收益题目链接:Exams/review2015count1k-HDLBitsmoduletop_module(inputclk,inputreset,output[9:0]q);always@(posedgeclk)beginif(reset)q=0)if(cnt<999)cnt

- 「HDLBits题解」Finite State Machines

UESTC_KS

HDLBits题解fpga开发Verilog

本专栏的目的是分享可以通过HDLBits仿真的Verilog代码以提供参考各位可同时参考我的代码和官方题解代码或许会有所收益题目链接:Fsm1-HDLBitsmoduletop_module(inputclk,inputareset,//AsynchronousresettostateBinputin,outputout);//parameterA=0,B=1;regstate,next_stat

- 【Verilog】HDLBits刷题 03 Verilog语言(2)(未完)

圆喵喵Won

fpga开发

二、模块(module)1.实例化Thefigurebelowshowsaverysimplecircuitwithasub-module.Inthisexercise,createoneinstanceofmodulemod_a,thenconnectthemodule'sthreepins(in1,in2,andout)toyourtop-levelmodule'sthreeports(wir

- 「HDLBits题解」Cellular automata

UESTC_KS

HDLBits题解fpga开发Verilog

本专栏的目的是分享可以通过HDLBits仿真的Verilog代码以提供参考各位可同时参考我的代码和官方题解代码或许会有所收益题目链接:Rule90-HDLBitsmoduletop_module(inputclk,inputload,input[511:0]data,output[511:0]q);always@(posedgeclk)beginif(load)q<=data;elseq<={1'

- 「HDLBits题解」Shift Registers

UESTC_KS

HDLBits题解fpga开发Verilog

本专栏的目的是分享可以通过HDLBits仿真的Verilog代码以提供参考各位可同时参考我的代码和官方题解代码或许会有所收益题目链接:Shift4-HDLBitsmoduletop_module(inputclk,inputareset,//asyncactive-highresettozeroinputload,inputena,input[3:0]data,outputreg[3:0]q);a

- 「HDLBits题解」Latches and Flip-Flops

UESTC_KS

HDLBits题解fpga开发Verilog

本专栏的目的是分享可以通过HDLBits仿真的Verilog代码以提供参考各位可同时参考我的代码和官方题解代码或许会有所收益题目链接:Dff-HDLBitsmoduletop_module(inputclk,//Clocksareusedinsequentialcircuitsinputd,outputregq);////Useaclockedalwaysblock//copydtoqatever

- 「HDLBits题解」Counters

UESTC_KS

HDLBits题解fpga开发Verilog

本专栏的目的是分享可以通过HDLBits仿真的Verilog代码以提供参考各位可同时参考我的代码和官方题解代码或许会有所收益题目链接:Count15-HDLBitsmoduletop_module(inputclk,inputreset,//Synchronousactive-highresetoutput[3:0]q);always@(posedgeclk)beginif(reset)q<=0;

- verilog语法进阶

FPGA中国创新中心

FPGA学习fpga开发verilogfpga硬件工程

文章目录前言一、always块(alwaysblock)二、if语句三、case语句四、casez语句五、三目运算(ternaryconditionaloperator)六、递减运算符(reduction)七、for循环语句八、实例化多个模块(generate)总结前言 本文是针对verilog基础语法做进一步的学,通过网站HDLbits中的代码和例子来展开本文要讨论的内容。HDLbits是一个

- 「HDLBits题解」Popcount255

UESTC_KS

HDLBits题解Verilog

本专栏的目的是分享可以通过HDLBits仿真的Verilog代码以提供参考各位可同时参考我的代码和官方题解代码或许会有所收益题目链接:Popcount255-HDLBitsmoduletop_module(input[254:0]in,outputreg[7:0]out);integeri;always@(*)beginout=0;for(i=0;i>i&1)out=out+1;elseout=o

- 「HDLBits题解」Adder100i

UESTC_KS

HDLBits题解Verilog

本专栏的目的是分享可以通过HDLBits仿真的Verilog代码以提供参考各位可同时参考我的代码和官方题解代码或许会有所收益题目链接:Adder100i-HDLBitsmoduletop_module(input[99:0]a,b,inputcin,output[99:0]cout,output[99:0]sum);add1Add0(a[0],b[0],cin,sum[0],cout[0]);ge

- 「HDLBits题解」Ringer

UESTC_KS

HDLBits题解Verilog

本专栏的目的是分享可以通过HDLBits仿真的Verilog代码以提供参考各位可同时参考我的代码和官方题解代码或许会有所收益题目链接:Ringer-HDLBitsmoduletop_module(inputring,inputvibrate_mode,outputringer,//Makesoundoutputmotor//Vibrate);assignmotor=vibrate_mode?(ri

- 「HDLBits题解」Bcdadd100

UESTC_KS

HDLBits题解Verilog

本专栏的目的是分享可以通过HDLBits仿真的Verilog代码以提供参考各位可同时参考我的代码和官方题解代码或许会有所收益题目链接:Bcdadd100-HDLBitsmoduletop_module(input[399:0]a,b,inputcin,outputcout,output[399:0]sum);wire[99:0]t;genvari;bcd_faddu0(a[3:0],b[3:0],

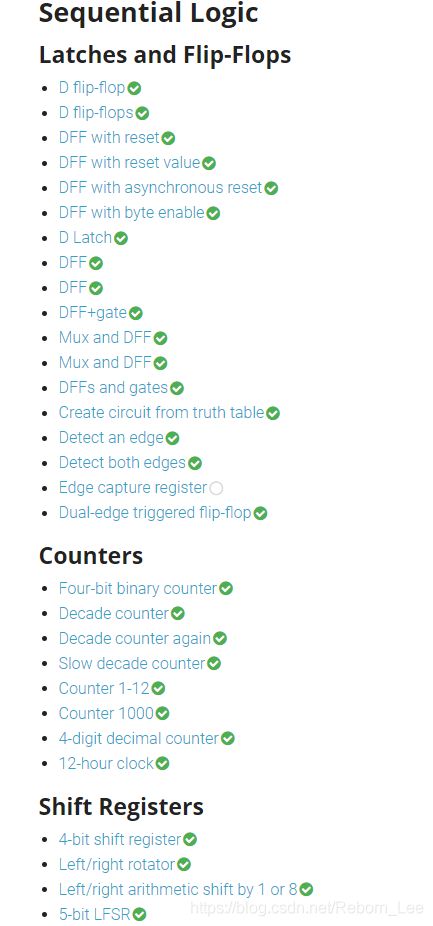

- 【Verilog】HDLBits题解——Circuits/Sequential Logic

wjh776a68

#Verilog入门verilogHDLBitsfpga

SequentialLogicLatchesandFlip-FlopsDflip-flop题目链接moduletop_module(inputclk,//Clocksareusedinsequentialcircuitsinputd,outputregq);////Useaclockedalwaysblock//copydtoqateverypositiveedgeofclk//Clockedal

- 【Verilog】HDLBits题解——Verilog Language

wjh776a68

#Verilog入门HDLBitsVerilog题解

BasicsSimplewire题目链接moduletop_module(inputin,outputout);assignout=in;endmoduleFourwires题目链接moduletop_module(inputa,b,c,outputw,x,y,z);assignw=a;assignx=b;assigny=b;assignz=c;endmoduleInverter题目链接modul

- 【Verilog】HDLBits题解——Circuits/Combinational Logic

wjh776a68

#Verilog入门VerilogHDLBits题解

CombinationalLogicBasicGatesWire题目链接moduletop_module(inputin,outputout);assignout=in;endmoduleGND题目链接moduletop_module(outputout);assignout=0;endmoduleNOR题目链接moduletop_module(inputin1,inputin2,outputou

- 【Verilog】HDLBits题解——Verification: Writing Testbenches

wjh776a68

#Verilog入门verilogHDLBitsfpga

Clock题目链接moduletop_module();regclk;initialbeginclk=0;forever#5clk=~clk;enddutdut_inst(.clk(clk));endmoduleTestbench1题目链接moduletop_module(outputregA,outputregB);////generateinputpatternshereinitialbegi

- HDLBits Bcdadd100

yezhangyinge

Verilog题解verilog

该题是根据已经写好的十进制加法器(BCDone-digitadder)module来构建100位十进制加法器BCDone-digitadder如下modulebcd_fadd{input[3:0]a,input[3:0]b,inputcin,outputcout,output[3:0]sum);分析显然可以根据二进制的100位加法器的思路,先进行初始化,但是此时我们无法使用简单的寄存器操作来实现功

- HDLbits Conwaylife题目的一种解法

WaterSplash

fpgaverilog

前言最近在刷HDLBits准备今年的提前批和人秋招,目前刷到有限状态机后,发现前面的大部分题目比较基础。目前比较有难度和有意思的题目就是Conwaylife,二维元胞自动机。这里仅提供笔者自己的解法。解题思路比较好想到的方法就是暴力枚举所有情况,给出该情况下所有的相邻坐标。思考过后觉得暴力枚举容易出现遗漏的情况。有没有一种通用的方法可以处理所有坐标呢。参考生命游戏的前两道题,使用另外两个向量,表示

- 「HDLBits题解」Always casez

UESTC_KS

HDLBits题解fpga开发Verilog

本专栏的目的是分享可以通过HDLBits仿真的Verilog代码以提供参考各位可同时参考我的代码和官方题解代码或许会有所收益题目链接:Alwayscasez-HDLBits//synthesisverilog_input_versionverilog_2001moduletop_module(input[7:0]in,outputreg[2:0]pos);always@(*)begincasez(

- 「HDLBits题解」Always nolatches

UESTC_KS

HDLBits题解Verilog

本专栏的目的是分享可以通过HDLBits仿真的Verilog代码以提供参考各位可同时参考我的代码和官方题解代码或许会有所收益题目链接:Alwaysnolatches-HDLBits//synthesisverilog_input_versionverilog_2001moduletop_module(input[15:0]scancode,outputregleft,outputregdown,o

- 「HDLBits题解」Module cseladd

UESTC_KS

HDLBits题解fpga开发Verilog

本专栏的目的是分享可以通过HDLBits仿真的Verilog代码以提供参考各位可同时参考我的代码和官方题解代码或许会有所收益题目链接:Modulecseladd-HDLBitsmoduletop_module(input[31:0]a,input[31:0]b,output[31:0]sum);wirecout1,cout2,cout3;wire[15:0]t1,t2,t3,t4;reg[15:0

- 如何用ruby来写hadoop的mapreduce并生成jar包

wudixiaotie

mapreduce

ruby来写hadoop的mapreduce,我用的方法是rubydoop。怎么配置环境呢:

1.安装rvm:

不说了 网上有

2.安装ruby:

由于我以前是做ruby的,所以习惯性的先安装了ruby,起码调试起来比jruby快多了。

3.安装jruby:

rvm install jruby然后等待安

- java编程思想 -- 访问控制权限

百合不是茶

java访问控制权限单例模式

访问权限是java中一个比较中要的知识点,它规定者什么方法可以访问,什么不可以访问

一:包访问权限;

自定义包:

package com.wj.control;

//包

public class Demo {

//定义一个无参的方法

public void DemoPackage(){

System.out.println("调用

- [生物与医学]请审慎食用小龙虾

comsci

生物

现在的餐馆里面出售的小龙虾,有一些是在野外捕捉的,这些小龙虾身体里面可能带有某些病毒和细菌,人食用以后可能会导致一些疾病,严重的甚至会死亡.....

所以,参加聚餐的时候,最好不要点小龙虾...就吃养殖的猪肉,牛肉,羊肉和鱼,等动物蛋白质

- org.apache.jasper.JasperException: Unable to compile class for JSP:

商人shang

maven2.2jdk1.8

环境: jdk1.8 maven tomcat7-maven-plugin 2.0

原因: tomcat7-maven-plugin 2.0 不知吃 jdk 1.8,换成 tomcat7-maven-plugin 2.2就行,即

<plugin>

- 你的垃圾你处理掉了吗?GC

oloz

GC

前序:本人菜鸟,此文研究学习来自网络,各位牛牛多指教

1.垃圾收集算法的核心思想

Java语言建立了垃圾收集机制,用以跟踪正在使用的对象和发现并回收不再使用(引用)的对象。该机制可以有效防范动态内存分配中可能发生的两个危险:因内存垃圾过多而引发的内存耗尽,以及不恰当的内存释放所造成的内存非法引用。

垃圾收集算法的核心思想是:对虚拟机可用内存空间,即堆空间中的对象进行识别

- shiro 和 SESSSION

杨白白

shiro

shiro 在web项目里默认使用的是web容器提供的session,也就是说shiro使用的session是web容器产生的,并不是自己产生的,在用于非web环境时可用其他来源代替。在web工程启动的时候它就和容器绑定在了一起,这是通过web.xml里面的shiroFilter实现的。通过session.getSession()方法会在浏览器cokkice产生JESSIONID,当关闭浏览器,此

- 移动互联网终端 淘宝客如何实现盈利

小桔子

移動客戶端淘客淘寶App

2012年淘宝联盟平台为站长和淘宝客带来的分成收入突破30亿元,同比增长100%。而来自移动端的分成达1亿元,其中美丽说、蘑菇街、果库、口袋购物等App运营商分成近5000万元。 可以看出,虽然目前阶段PC端对于淘客而言仍旧是盈利的大头,但移动端已经呈现出爆发之势。而且这个势头将随着智能终端(手机,平板)的加速普及而更加迅猛

- wordpress小工具制作

aichenglong

wordpress小工具

wordpress 使用侧边栏的小工具,很方便调整页面结构

小工具的制作过程

1 在自己的主题文件中新建一个文件夹(如widget),在文件夹中创建一个php(AWP_posts-category.php)

小工具是一个类,想侧边栏一样,还得使用代码注册,他才可以再后台使用,基本的代码一层不变

<?php

class AWP_Post_Category extends WP_Wi

- JS微信分享

AILIKES

js

// 所有功能必须包含在 WeixinApi.ready 中进行

WeixinApi.ready(function(Api) {

// 微信分享的数据

var wxData = {

&nb

- 封装探讨

百合不是茶

JAVA面向对象 封装

//封装 属性 方法 将某些东西包装在一起,通过创建对象或使用静态的方法来调用,称为封装;封装其实就是有选择性地公开或隐藏某些信息,它解决了数据的安全性问题,增加代码的可读性和可维护性

在 Aname类中申明三个属性,将其封装在一个类中:通过对象来调用

例如 1:

//属性 将其设为私有

姓名 name 可以公开

- jquery radio/checkbox change事件不能触发的问题

bijian1013

JavaScriptjquery

我想让radio来控制当前我选择的是机动车还是特种车,如下所示:

<html>

<head>

<script src="http://ajax.googleapis.com/ajax/libs/jquery/1.7.1/jquery.min.js" type="text/javascript"><

- AngularJS中安全性措施

bijian1013

JavaScriptAngularJS安全性XSRFJSON漏洞

在使用web应用中,安全性是应该首要考虑的一个问题。AngularJS提供了一些辅助机制,用来防护来自两个常见攻击方向的网络攻击。

一.JSON漏洞

当使用一个GET请求获取JSON数组信息的时候(尤其是当这一信息非常敏感,

- [Maven学习笔记九]Maven发布web项目

bit1129

maven

基于Maven的web项目的标准项目结构

user-project

user-core

user-service

user-web

src

- 【Hive七】Hive用户自定义聚合函数(UDAF)

bit1129

hive

用户自定义聚合函数,用户提供的多个入参通过聚合计算(求和、求最大值、求最小值)得到一个聚合计算结果的函数。

问题:UDF也可以提供输入多个参数然后输出一个结果的运算,比如加法运算add(3,5),add这个UDF需要实现UDF的evaluate方法,那么UDF和UDAF的实质分别究竟是什么?

Double evaluate(Double a, Double b)

- 通过 nginx-lua 给 Nginx 增加 OAuth 支持

ronin47

前言:我们使用Nginx的Lua中间件建立了OAuth2认证和授权层。如果你也有此打算,阅读下面的文档,实现自动化并获得收益。SeatGeek 在过去几年中取得了发展,我们已经积累了不少针对各种任务的不同管理接口。我们通常为新的展示需求创建新模块,比如我们自己的博客、图表等。我们还定期开发内部工具来处理诸如部署、可视化操作及事件处理等事务。在处理这些事务中,我们使用了几个不同的接口来认证:

&n

- 利用tomcat-redis-session-manager做session同步时自定义类对象属性保存不上的解决方法

bsr1983

session

在利用tomcat-redis-session-manager做session同步时,遇到了在session保存一个自定义对象时,修改该对象中的某个属性,session未进行序列化,属性没有被存储到redis中。 在 tomcat-redis-session-manager的github上有如下说明: Session Change Tracking

As noted in the &qu

- 《代码大全》表驱动法-Table Driven Approach-1

bylijinnan

java算法

关于Table Driven Approach的一篇非常好的文章:

http://www.codeproject.com/Articles/42732/Table-driven-Approach

package com.ljn.base;

import java.util.Random;

public class TableDriven {

public

- Sybase封锁原理

chicony

Sybase

昨天在操作Sybase IQ12.7时意外操作造成了数据库表锁定,不能删除被锁定表数据也不能往其中写入数据。由于着急往该表抽入数据,因此立马着手解决该表的解锁问题。 无奈此前没有接触过Sybase IQ12.7这套数据库产品,加之当时已属于下班时间无法求助于支持人员支持,因此只有借助搜索引擎强大的

- java异常处理机制

CrazyMizzz

java

java异常关键字有以下几个,分别为 try catch final throw throws

他们的定义分别为

try: Opening exception-handling statement.

catch: Captures the exception.

finally: Runs its code before terminating

- hive 数据插入DML语法汇总

daizj

hiveDML数据插入

Hive的数据插入DML语法汇总1、Loading files into tables语法:1) LOAD DATA [LOCAL] INPATH 'filepath' [OVERWRITE] INTO TABLE tablename [PARTITION (partcol1=val1, partcol2=val2 ...)]解释:1)、上面命令执行环境为hive客户端环境下: hive>l

- 工厂设计模式

dcj3sjt126com

设计模式

使用设计模式是促进最佳实践和良好设计的好办法。设计模式可以提供针对常见的编程问题的灵活的解决方案。 工厂模式

工厂模式(Factory)允许你在代码执行时实例化对象。它之所以被称为工厂模式是因为它负责“生产”对象。工厂方法的参数是你要生成的对象对应的类名称。

Example #1 调用工厂方法(带参数)

<?phpclass Example{

- mysql字符串查找函数

dcj3sjt126com

mysql

FIND_IN_SET(str,strlist)

假如字符串str 在由N 子链组成的字符串列表strlist 中,则返回值的范围在1到 N 之间。一个字符串列表就是一个由一些被‘,’符号分开的自链组成的字符串。如果第一个参数是一个常数字符串,而第二个是type SET列,则 FIND_IN_SET() 函数被优化,使用比特计算。如果str不在strlist 或st

- jvm内存管理

easterfly

jvm

一、JVM堆内存的划分

分为年轻代和年老代。年轻代又分为三部分:一个eden,两个survivor。

工作过程是这样的:e区空间满了后,执行minor gc,存活下来的对象放入s0, 对s0仍会进行minor gc,存活下来的的对象放入s1中,对s1同样执行minor gc,依旧存活的对象就放入年老代中;

年老代满了之后会执行major gc,这个是stop the word模式,执行

- CentOS-6.3安装配置JDK-8

gengzg

centos

JAVA_HOME=/usr/java/jdk1.8.0_45

JRE_HOME=/usr/java/jdk1.8.0_45/jre

PATH=$PATH:$JAVA_HOME/bin:$JRE_HOME/bin

CLASSPATH=.:$JAVA_HOME/lib/dt.jar:$JAVA_HOME/lib/tools.jar:$JRE_HOME/lib

export JAVA_HOME

- 【转】关于web路径的获取方法

huangyc1210

Web路径

假定你的web application 名称为news,你在浏览器中输入请求路径: http://localhost:8080/news/main/list.jsp 则执行下面向行代码后打印出如下结果: 1、 System.out.println(request.getContextPath()); //可返回站点的根路径。也就是项

- php里获取第一个中文首字母并排序

远去的渡口

数据结构PHP

很久没来更新博客了,还是觉得工作需要多总结的好。今天来更新一个自己认为比较有成就的问题吧。 最近在做储值结算,需求里结算首页需要按门店的首字母A-Z排序。我的数据结构原本是这样的:

Array

(

[0] => Array

(

[sid] => 2885842

[recetcstoredpay] =&g

- java内部类

hm4123660

java内部类匿名内部类成员内部类方法内部类

在Java中,可以将一个类定义在另一个类里面或者一个方法里面,这样的类称为内部类。内部类仍然是一个独立的类,在编译之后内部类会被编译成独立的.class文件,但是前面冠以外部类的类名和$符号。内部类可以间接解决多继承问题,可以使用内部类继承一个类,外部类继承一个类,实现多继承。

&nb

- Caused by: java.lang.IncompatibleClassChangeError: class org.hibernate.cfg.Exten

zhb8015

maven pom.xml关于hibernate的配置和异常信息如下,查了好多资料,问题还是没有解决。只知道是包冲突,就是不知道是哪个包....遇到这个问题的分享下是怎么解决的。。

maven pom:

<dependency>

<groupId>org.hibernate</groupId>

<ar

- Spark 性能相关参数配置详解-任务调度篇

Stark_Summer

sparkcachecpu任务调度yarn

随着Spark的逐渐成熟完善, 越来越多的可配置参数被添加到Spark中来, 本文试图通过阐述这其中部分参数的工作原理和配置思路, 和大家一起探讨一下如何根据实际场合对Spark进行配置优化。

由于篇幅较长,所以在这里分篇组织,如果要看最新完整的网页版内容,可以戳这里:http://spark-config.readthedocs.org/,主要是便

- css3滤镜

wangkeheng

htmlcss

经常看到一些网站的底部有一些灰色的图标,鼠标移入的时候会变亮,开始以为是js操作src或者bg呢,搜索了一下,发现了一个更好的方法:通过css3的滤镜方法。

html代码:

<a href='' class='icon'><img src='utv.jpg' /></a>

css代码:

.icon{-webkit-filter: graysc