HDLBits刷题合集—19 Finite State Machines-5

HDLBits刷题合集—19 Finite State Machines-5

HDLBits-146 Exams/m2014 q6b

Problem Statement

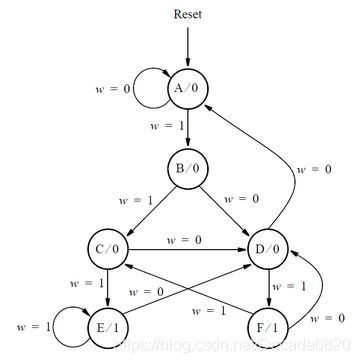

考虑下面显示的状态机,它有一个输入w和一个输出z。

假设你希望使用三个触发器和状态码y [3:1] = 000、001,…,101分别用于状态A,B,…,F来实现FSM。 显示此FSM的状态分配表。 推导触发器y[2]的次态表达式。

仅实现y[2]的下一状态逻辑。

状态转换表如下所示:

module top_module (

input [3:1] y,

input w,

output Y2);

parameter A=3'b000, B=3'b001, C=3'b010, D=3'b011, E=3'b100, F=3'b101;

reg [3:1] state_next;

always @(*) begin

case (y)

A : begin

if (w) state_next <= A;

else state_next <= B;

end

B : begin

if (w) state_next <= D;

else state_next <= C;

end

C : begin

if (w) state_next <= D;

else state_next <= E;

end

D : begin

if (w) state_next <= A;

else state_next <= F;

end

E : begin

if (w) state_next <= D;

else state_next <= E;

end

F : begin

if (w) state_next <= D;

else state_next <= C;

end

default : state_next <= A;

endcase

end

assign Y2 = state_next[2];

endmodule

HDLBits-147 Exams/m2014 q6c

Problem Statement

考虑下面显示的状态机,它有一个输入w和一个输出z。

对于此部分,假设使用独热码分别为状态A,B,…,F编码,状态分配为y [6:1] = 000001、000010、000100、001000、010000、100000。

编写次态信号y2和y4的逻辑表达式。

代码如下:

module top_module (

input [6:1] y,

input w,

output Y2,

output Y4);

parameter A=6'b000001, B=6'b000010, C=6'b000100;

parameter D=6'b001000, E=6'b010000, F=6'b100000;

reg [6:1] state_next;

always @(*) begin

case (y)

A : begin

if (w) state_next <= A;

else state_next <= B;

end

B : begin

if (w) state_next <= D;

else state_next <= C;

end

C : begin

if (w) state_next <= D;

else state_next <= E;

end

D : begin

if (w) state_next <= A;

else state_next <= F;

end

E : begin

if (w) state_next <= D;

else state_next <= E;

end

F : begin

if (w) state_next <= D;

else state_next <= C;

end

default : state_next <= A;

endcase

end

assign Y2 = y[1] & ~w;

assign Y4 = (y[2] & w) | (y[3] & w) | (y[5] & w) | (y[6] & w);

endmodule

HDLBits-148 Exams/m2014 q6

Problem Statement

考虑下面显示的状态机,它有一个输入w和一个输出z。

module top_module (

input clk,

input reset, // synchronous reset

input w,

output z);

parameter A=0, B=1, C=2, D=3, E=4, F=5;

reg [2:0] state, state_next;

always @(*) begin

case (state)

A : begin

if (w) state_next = A;

else state_next = B;

end

B : begin

if (w) state_next = D;

else state_next = C;

end

C : begin

if (w) state_next = D;

else state_next = E;

end

D : begin

if (w) state_next = A;

else state_next = F;

end

E : begin

if (w) state_next = D;

else state_next = E;

end

F : begin

if (w) state_next = D;

else state_next = C;

end

default : state_next = A;

endcase

end

always @(posedge clk)

begin

if (reset) state <= A;

else state <= state_next;

end

assign z = (state == E) | (state == F);

endmodule

HDLBits-149 Exams/2012 q2fsm

编写代表此FSM的完整Verilog代码。 对状态表和状态触发器使用单独的Always块。 使用连续赋值语句或Always块描述FSM的输出z。 状态编码随你心意。

代码如下:

module top_module (

input clk,

input reset, // Synchronous active-high reset

input w,

output z

);

parameter A=0, B=1, C=2, D=3, E=4, F=5;

reg [2:0] state, state_next;

always @(*) begin

case (state)

A : begin

if (w) state_next <= B;

else state_next <= A;

end

B : begin

if (w) state_next <= C;

else state_next <= D;

end

C : begin

if (w) state_next <= E;

else state_next <= D;

end

D : begin

if (w) state_next <= F;

else state_next <= A;

end

E : begin

if (w) state_next <= E;

else state_next <= D;

end

F : begin

if (w) state_next <= C;

else state_next <= D;

end

default : state_next <= A;

endcase

end

always @(posedge clk)

begin

if (reset) state <= A;

else state <= state_next;

end

assign z = (state == E) | (state == F);

endmodule

HDLBits-150 Exams/2012 q2b

Problem Statement

考虑下面显示的状态机。

假设使用独热码进行状态分配,y [5:0] = 000001(A),000010(B),000100(C),001000(D),010000(E),100000(F)

写出状态触发器y [1]输入Y1的逻辑表达式。

写出状态触发器y [3]输入Y3的逻辑表达式。

代码如下:

module top_module (

input [5:0] y,

input w,

input clk,

input reset,

output Y1,

output Y3

);

parameter A=6'b000001, B=6'b000010, C=6'b000100;

parameter D=6'b001000, E=6'b010000, F=6'b100000;

reg [5:0] state, state_next;

always @(*) begin

case (state)

A : begin

if (w) state_next <= B;

else state_next <= A;

end

B : begin

if (w) state_next <= C;

else state_next <= D;

end

C : begin

if (w) state_next <= E;

else state_next <= D;

end

D : begin

if (w) state_next <= F;

else state_next <= A;

end

E : begin

if (w) state_next <= E;

else state_next <= D;

end

F : begin

if (w) state_next <= C;

else state_next <= D;

end

default : state_next <= A;

endcase

end

always @(posedge clk)

begin

if (reset) state <= A;

else state <= state_next;

end

assign Y1 = w & y[0];

assign Y3 = ~w & (y[1] | y[2] | y[4] | y[5]);

endmodule

HDLBits-151 Exams/2013 q2afsm

Problem Statement

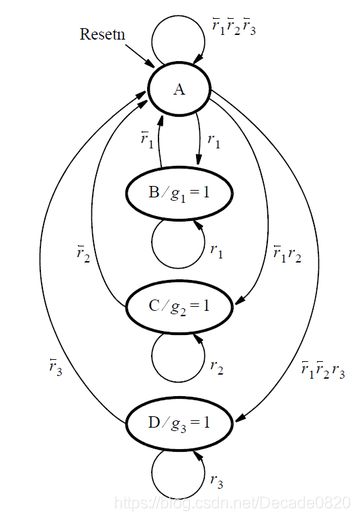

考虑以下状态图描述的FSM:

该FSM充当仲裁器电路,该电路控制三个请求设备对某种类型资源的访问。每个设备通过设置信号r [i] = 1来请求资源,其中r [i]为r [1],r [2]或r [3]。

每个r [i]是FSM的输入信号,代表三个设备之一。只要没有请求,FSM就会保持状态A。当发生一个或多个请求时,FSM决定哪个设备接收到使用该资源的授权,并更改为将该设备的g [i]信号设置为1的状态。

每个g [i]是FSM的输出。有一个优先级系统,即设备1的优先级高于设备2的优先级,而设备3的优先级最低。因此,例如,当FSM处于状态A时,如果设备3是唯一发出请求的设备,则设备3将仅接收授权。一旦设备(即,FSM给了设备i)授权,该设备将继续接收授权,只要它的请求r [i] = 1。

编写代表此FSM的完整Verilog代码,对状态表和状态触发器使用单独的Always块。使用连续赋值语句或Always块(自行决定)描述FSM输出g [i]。状态分配随你所意。

代码如下:

module top_module (

input clk,

input resetn, // active-low synchronous reset

input [3:1] r, // request

output [3:1] g // grant

);

parameter A=0, B=1, C=2, D=3;

reg [1:0] state, state_next;

always @(*) begin

case (state)

A : begin

if (r[1])

state_next <= B;

else if (~r[1] & r[2])

state_next <= C;

else if (~r[1] & ~r[2] &r[3])

state_next <= D;

else

state_next <= A;

end

B : begin

if (r[1]) state_next <= B;

else state_next <= A;

end

C : begin

if (r[2]) state_next <= C;

else state_next <= A;

end

D : begin

if (r[3]) state_next <= D;

else state_next <= A;

end

default : state_next <= A;

endcase

end

always @(posedge clk)

begin

if (!resetn) state <= A;

else state <= state_next;

end

assign g = {state == D,state == C,state == B};

endmodule

HDLBits-152 Exams/2013 q2bfsm

Problem Statement

考虑用于控制某种类型电动机的有限状态机。 FSM具有来自电动机的输入x和y,并产生控制电动机的输出f和g。还有一个时钟输入clk和一个复位输入resetn。

FSM必须按以下方式工作。只要复位输入有效,FSM就会保持在开始状态(称为状态A)。取消复位信号后,在下一个时钟沿之后,FSM必须在一个时钟周期内将输出f设置为1。然后,FSM必须监视x输入。当x在三个连续的时钟周期中产生值1,0,1时,则应在下一个时钟周期将g设置为1。在保持g = 1的同时,FSM必须监视y输入。如果y在最多两个时钟周期内的值为1,则FSM应永久保持g = 1(即直到复位)。但是,如果y在两个时钟周期内未变为1,则FSM应永久设置g = 0(直到复位)。

代码如下:

module top_module (

input clk,

input resetn, // active-low synchronous reset

input x,

input y,

output f,

output g

);

parameter A=0, B=1, C=2, D=3, E=4, F=5, G=6,H=7, I=8;

reg [3:0] state, state_next;

always @(*) begin

case (state)

A : begin

state_next <= B;

end

B : begin

state_next <= C;

end

C : begin

if (x) state_next <= D;

else state_next <= C;

end

D : begin

if (x) state_next <= D;

else state_next <= E;

end

E : begin

if (x) state_next <= F;

else state_next <= C;

end

F : begin

if (y) state_next <= H;

else state_next <= G;

end

G : begin

if (y) state_next <= H;

else state_next <= I;

end

H : begin

state_next <= H;

end

I : begin

state_next <= I;

end

endcase

end

always @(posedge clk)

begin

if (!resetn) state <= A;

else state <= state_next;

end

assign f = (state == B);

assign g = (state == F) | (state == H) | (state == G);

endmodule

Note

新手一枚,主要分享博客,记录学习过程,后期参考大佬代码或思想会一一列出。欢迎大家批评指正!